반도체 수준의 FMEDA 수행 방안

Copyright Ⓒ 2021 KSAE / 183-10

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License(http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium provided the original work is properly cited.

Abstract

Quantitative evaluation of random failure for semiconductor elements is essential in the development of automotive semiconductors that comply with the ASIL B or higher functional safety ISO 26262 standard. The most preferred method for performing these quantitative assessments is the FMEDA analysis technique. FMEDA, along with the introduction of ISO 26262, is a quantitative safety analysis that has been used in the overall automotive industry for many years. However, the domestic semiconductor industry has little practical experience with FMEDA, perhaps because it is in the early process of introducing the functional safety ISO 26262. Moreover, since there are few FMEDA-related data suitable for the semiconductor level, it is difficult to understand and apply to semiconductor analysis. The aim of this paper is to gain a better understanding of the quantitative safety analysis at the semiconductor level by presenting a method of performing the FMEDA at the semiconductor level from a practical point of view.

Keywords:

Functional safety, ISO 26262, Random hardware failure, Base failure rate, Failure modes effects and diagnostics analysis, Quantitative safety analysis of semiconductor level, Semiconductor키워드:

기능안전, 자동차 기능 안전성 국제 표준, 하드웨어 우발 고장, 기본 고장률, 고장모드 영향 및 진단 분석, 반도체 수준의 정량적 안전분석, 반도체1. 서 론

자동차 산업은 기존 기계류 중심의 개발 환경에서, E/E System 즉, 전기전자 시스템으로 개발 패러다임이 급격하게 변화하고 있다. 요즘 자동차 산업에서의 최신 트렌드는 당연 ADS(자율 주행 시스템)1) 일 것이다. 자율 주행 시스템은 움직이는 컴퓨터와 다름이 없다고 해도 과언이 아니다. 이러한 변화 속에서 E/E System의 근간이 되는 반도체의 중요성은 논란의 여지가 없다. 그러하기 때문에, 2018년 12월에 발표된 기능안전 ISO 26262 2nd에서는 새로이 반도체 부분을 추가하였다. “ISO 26262 Part 11: Guidelines on application of ISO 26262 to semiconductors”2)가 그것이다.

ISO 26262 Part 112)은 반도체에 대한 기능안전 ISO 26262:2018 적용 가이드라인으로서 Part 3, 4, 5, 6, 7과 같은 핵심 파트와 달리 요구사항은 아니나, 기능안전 반도체 적용에 있어서 참고할 만한 지침을 제공한다. 이 지침에는 기능안전을 준수하는 반도체의 개발은 기본적으로 Part 5 하드웨어 개발 요구사항3)을 준수할 것을 권고하고 있으며, 필요에 따라서는 Part 4 시스템 개발 요구사항4) 이나 Part 6 소프트웨어 개발 요구사항5) 역시 적절히 테일러링 하여 수행할 것을 권고한다. 어찌 됐든 Part 5의 하드웨어 개발 요구 사항3)들을 준수해야 하므로 반도체에 대한 우발 고장을 정량적으로 평가하여야 한다.

본 논문은 이러한 정량적 평가에 있어서 일반적으로 사용되는 FMEDA 기법을 반도체 수준에 맞춰 소개하고, 이에 대한 작성 절차를 ISO 26262-11:2018 4.6.2.1.12)에서 적용된 IEC TR 62380:20046)를 기반으로 설명한다.

2. 반도체 분석의 세분화 수준

정성적이든 정량적이든지 간에 안전 분석을 위한 주요 측면 중 하나는 분석을 기반으로 하는 계층 구조의 수준을 적절하게 식별하는 것이다. 대개의 경우, 분석의 세분화 수준을 낮추는 것이 고장 모드 및 고장 모드 분포를 더 잘 이해하는 것으로 볼 수 있다.2) 하지만, 그렇다고 필요 이상으로 분석의 수준을 깊게 할 경우, 개발 과정에서 너무 많은 리소스가 요구되어 개발 비용 및 제품 출시 일정 등에 영향을 줄 수 있으므로 주의가 요구된다.

2.1 제어기/반도체의 구성 분류 및 ‘Part’에 대한 고찰

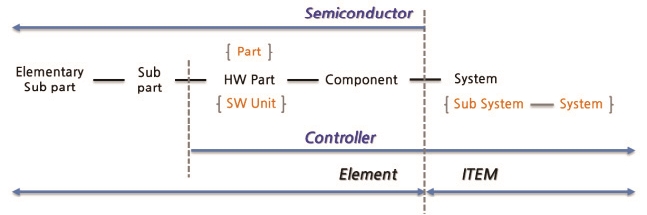

아래 Fig. 1은 제어기 및 반도체의 구성 분류를 보여주는 그림으로서, ISO26262-10:2011 Fig. 3,7) ISO2626-10:2018 Fig. 3, Fig. 4,8) ISO26262-11 Fig. 22)를 참조하였다.

Fig. 1에서 보다시피 Controller 수준에서의 최하위 구성 단위는 ‘HW Part’이다. ISO 26262:2011 1st는 주로 Controller 중심으로 기술하였기 때문에, ‘Part’를 ‘소자’(Passive 부품류: 저항, 캐패시터, 인덕터 / Discrete 부품류: 다이오드, 트랜지스터, FET류)라고 번역될 수 있었으나,9) ISO 26262:2018 2nd에서 반도체 부분이 추가됨으로써, ‘Part’를 ‘소자’라고 딱히 번역하기 어려운 상황이 되었다. 이 경우의 ‘Part’는 반도체 내부를 구성하는 엘리먼트들인 CPU, ADC, PWM, TIMER 등을 지칭하는 것이기 때문이다. 그러므로 본문에서는 ‘Part’를 ‘소자’ 또는 ‘부품’이라 하지 않고 ‘Part’ 또는 ‘파트’라고 기술한다.

2.2 반도체 구성 엘리먼트에 대한 분류

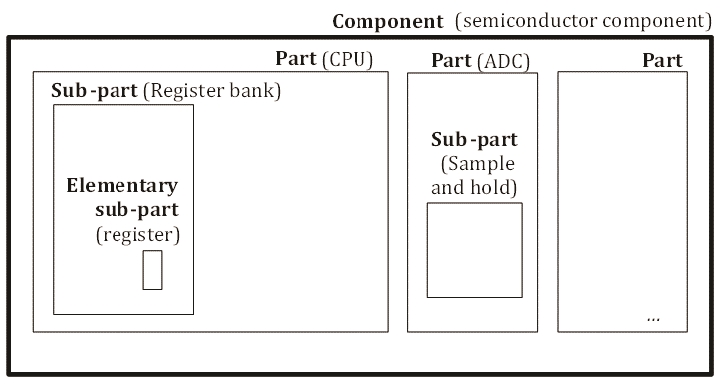

아래 Fig. 2는 ISO 26262-11:2018에서 보여준 반도체 컴포넌트의 일반적인 구성이다.2)

Fig. 2를 보다시피 반도체 컴포넌트는 다음과 같은 구성 요소로 분해될 수 있다.2) 참고로, IP(지적 재산)에는 Fig. 2에 표현된 Part, Sub-part, Elementary sub-part를 포함한다.

1) Component: 논리적/기술적으로 분리가 가능하고 하나 이상의 Part로 구성된 엘리먼트

2) Part: 반도체 내부의 CPU, ADC, PWM, Timer 등을 가리키는 구성 엘리먼트

3) Sub-part: Part의 하위 수준으로서, Part를 구성하는 구성 엘리먼트

4) Elementary sub-part: 레지스터와 같은 기초 하위 엘리먼트

분석의 세분화 수준은 반도체 아키텍처가 반도체 구성 요소의 어느 부분까지 표현하고 있는지에 따라 달라질 수 있겠으나, 적어도 반도체 수준의 정량적 분석의 최소 깊이는 Sub-part일 것을 권장한다.

3. 반도체 수준의 FMEDA 수행

다음은 반도체 수준의 FMEDA 수행 방안을 기술한 내용이다. 참고로 본문의 3.1∼3.7항은 작업 순서를 의미하는 것이 아니기 때문에, 한 단계가 끝나야만 다음 단계로 진행할 수 있는 구조가 아니다. 즉, FMEDA 수행 과정에서 각 항은 언제든 반복 및 갱신될 수 있다. 그리고 3.1∼3.6항은 3.7항을 수행하기 위한 준비 과정으로 볼 수 있으며, 사용된 모든 예시는 이해를 돕기 위해 작성된 것이다.

3.1 최상위 안전 요구사항의 할당

1) 분석 대상 반도체에 할당된 안전 요구사항과 관련된 반도체 안전 관련 엘리먼트들을 식별하고,

2) 식별된 안전 관련 엘리먼트들의 고장을 분석하여 안전 고장, 단일점 고장, 잔존 고장, 다중점 잠재 고장과 같은, 고장 모드를 분류하기 위함이다.

1) 하나의 안전 목표로부터 파생된 안전 요구사항들만을 기술한다.

2) 다른 안전 목표로부터 파생된 안전 요구사항들은 별도의 FMEDA 분석에서 다룬다. 이는 안전 목표로부터 파생된 최상위 안전 요구사항에 따른 반도체 엘리먼트의 고장 모드 분류를 정확하게 하기 위함이며, 또한 정량적 목표값을 하나로 가지기 위함이다.

3) 되도록 하위 안전 요구 사항들을 포괄할 수 있는 상위 요구 사항을 기술한다.

4) 필요시 안전목표(SG) 및/또는 ASIL 등급을 병행하여 기입한다.

1) TSR1: 두 입력을 비교하여 차이 값이 허용치 이상일 경우, High side와 Low side의 출력 신호를 100 ms 이내로 차단시켜야 한다(ASIL B).

2) TSR2: 칩 내부의 에러를 검출하면, 진단 코드를 100 ms 이내로 출력해야 한다.(ASIL B)

3.2 구조 분석(Structure Analysis)

1) 반도체 아키텍처를 상세 분석하여 분석 대상의 이해를 돕고,

2) 반도체를 구성하는 엘리먼트들에 대한 기본 고장률(BFR) 계산 시 필요한 정보를 제공하기 위함이다.

위의 목적을 위해 반도체 아키텍처로부터 Table 1과 같은 반도체구조 분석 테이블을 작성한다. 다음은 Table 1에 기술할 내용을 설명한다.

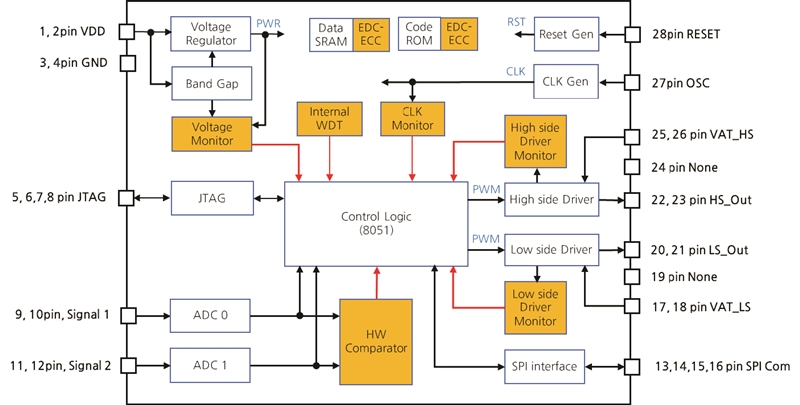

1) Part/Sub-part name: 분석 대상 반도체 엘리먼트의 이름이다. 일관성을 위해 아래 Fig. 3 반도체 아키텍처에 기술된 블록 이름과 같아야 한다.

2) Volt: 반도체 엘리먼트에서 사용되는 전압을 기술한다. 사용 전압에 따라 Transient fault(일시적인 결함) 값이 달라짐으로, 이 값은 일시적 결함률을 구할 때 사용한다.

3) Description: 분석 대상 반도체 엘리먼트에 대한 기능을 기술한다.

4) Parts type: 분석 대상 반도체 엘리먼트의 Type을 기술한다. Type은 ‘Digital part’, ‘Analog part’, ‘Mixed part’가 있다.

5) Semiconductor technology: 분석 대상 반도체 엘리먼트별로 적용된 반도체 기술 유형(Semiconductor technology)을 기술한다. 예를 들어, Fig. 3과 같은 반도체 Architecture가 주어진 경우, IEC TR 62380 Table 166)의 분류에 따라 Digital parts는 Digital circuits에 해당되며, Analog low voltage Parts는 Linear circuits low voltage (<6 V)에 해당되고, Analog high voltage parts는 Linear circuits high voltage (>=6 V)에 해당된다.

6) Number of gate: 분석 대상 반도체 엘리먼트에 대한 등가 게이트 개수를 기술한다.

7) Number of transistor: 분석 대상 반도체 엘리먼트에 대한 등가 트랜지스터 개수를 기술한다.

3.3 안전 메커니즘 및 진단 커버리지

1) 안전 요구사항을 위배할 가능성이 있는 반도체 엘리먼트의 고장 모드를 방지하거나 회피하기 위한 기술적 수단인 안전 메커니즘에 대한 기능 및 속성을 명세하고,

2) 안전 메커니즘의 진단 커버리지 값을 도출하기 위함이다.

위의 목적을 위해 아래의 Table 2를 작성한다. 다음은 Table 2에 기술할 내용을 설명한다.

1) Define of safety status at IC level : 반도체 수준의 안전 상태를 정의한다.

2) SM No : 안전 메커니즘의 ID를 기입한다.

3) SM Name : 안전 메커니즘 이름이다.

4) Detailed description : 안전 메커니즘에 대한 설명이다. 되도록 기능을 포함하는 작동 원리를 기술한다. 단일점 결함을 방지하는 안전 메커니즘 또는 잠재 결함을 방지하는 안전 메커니즘이 있으나, 설계 방식에 따라서 하나의 안전 메커니즘이 둘 모두를 방지할 수도 있다. 참고로 “효과적인 FMEDA 수행을 위한 안전 메커니즘의 작성 방안과 진단 커버리지의 산정 방안”10)에서는 안전 메커니즘 기술 및 진단 커버리지 산정에 관한 참고할 만한 정보를 제공한다.

5) Timing : 안전 메커니즘이 동작하는 주기를 기술한다. 안전 메커니즘은 하드웨어 방식의 상시 동작 방식, 클록 주기 방식, 소프트웨어 의한 일정 시간 주기 방식, 하드웨어 또는 소프트웨어 인터럽트에 의한 이벤트 방식, Power on/off시마다 한 번씩 동작하는 방식 등이 있다.

6) Type : 안전 메커니즘이 반도체 내부(Internal)에서 동작하는지 또는 반도체 외부(External)에서 동작하는지를 기술한다.

7) DC : 산정된 안전 메커니즘의 진단 커버리지 값을 ‘Avoidance of single point fault’ 및/또는 ‘Avoidance of latent fault’에 기술한다.

8) Rationale of evaluation : DC를 산출한 근거를 ‘Avoidance of single point fault’ 및/또는 ‘Avoidance of latent fault’에 기술한다. 해당 되는 경우, 결함 주입 시험에 의한 시험 결과를 포함한다.

아래 Table 2는 안전 메커니즘 및 진단 커버리지에 대한 내용을 기술한 예시이다. 참고로, SM-01, SM-03, SM-05, SM-06, SM-07, SM-08, SM-09, SM-011과 같은 안전 메커니즘에 대한 DC 산출에 있어서, 그 근거의 정당성을 증명해 줄 수 있는 세부적인 논리적 근거나 결함 주입 시험 결과는 본 예시에서 생략하였다. 이러한 세부적인 근거는 필요시 별도로 기술한다.

3.4 미션 프로파일

1) 반도체에 대한 현장 사용 환경과 조건에 관한 설정으로서, 반도체가 사용되는 환경의 온도, 반도체 사용 패턴 등을 정하고,

2) 이것을 반도체 엘리먼트 별 영구적인 기본 고장률 계산에 반영하기 위함이다.

1) 고객으로부터 전달받은 Mission profile을 우선적으로 사용해야 하나, 그렇지 않은 경우, 신뢰할 만한 고장률 데이터 북을 활용하여 적용한다. ISO 26262:2018에서 제시되고 현업에서 Mission profile을 참고할 수 있는 신뢰할 만한 고장률 데이터 북에는 IEC 61709,11) ISO 26262-11:2018 4.6.2.1.1 (IEC TR 62380:2004),2,6) FIDES 2009 EdA12) 등이 있다.

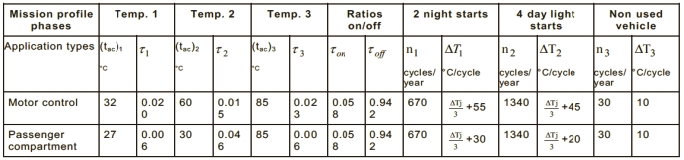

2) 아래 Table 3은 ISO 26262-11:2018 4.6.2.1.1(IEC TR 62380:2004)에서 제시된 자동차에 대한 Mission profile 로서 다음은 이에 대한 설명이다.2,6)

① IEC TR 62380의 Mission Profile은 연간 운용 사이클을 기반으로 하여 몇 가지 동질적인 동작 단계로 분해된다.

a. 장비가 노출되는 다양한 평균 외부 온도에서 동작하는 On/Off working phases.

b. 장비가 노출되는 다양한 평균 외부 온도에서 지속적으로 동작하는 Permanent working phases

c. 장비가 노출되는 다양한 평균 외부 온도에서 저장 또는 휴면하는 Storage or dormant phases

② 필요한 Parameters는 아래와 같다.

(tae)i : 장비(제어기)의 i번째 phase에서 장비(제어기)를 둘러싼 평균 외부 대기 온도. 프랑스 기후의 경우는 11 °C이며, 전 세계적인 기후에 대해 14 °C를 유지

(tac)i : i번째 phase에서(가장 중요한 것으로 간주되는) 컴포넌트(반도체) 주변 PCB의 평균 주변 온도.

tac = average temperature increases of the PCB near components + tae

τ i : (tac)i 온도 시 동작하는 시간의 연간 비율

τ on : 전원이 공급되어 동작하는 전체 시간의 연간 비율

τ off : 동작하지 않거나 저장/휴면 모드 상태로 있는 전체 연간 시간 비율

n i : 평균 온도 변동 ΔTi를 동반한 i번째 Phase에 일치하는 PCB의 컴포넌트에 의해 보이는 온도 사이클 수량

ΔTi : i 번째 단계에서 PCB의 구성 요소에서 볼 수 있는 열 변동의 평균 편차

On/Off working phases인 경우:

집적 회로 또는 discrete 소자인 경우라면, 접합 온도 상승이고, 수동 소자인 경우라면, 표면 온도 상승이다. 그 값의 3분의 1만이 ΔTi 계산에 고려된다. 따라서 고려해야 할 온도는 내부 온도에 대한 절충안이며, 일부 열 시뮬레이션은 이 값의 1/3이 적절하다는 것을 보여준다.

Storage or Permanent working phase인 경우:

만일 이 값이 3 °C보다 낮으면, 이 값의 열 기계적 응력은 COFFIN-MANSON 방정식에서 열적으로 독립적이라는 조건을 고려하여 ΔTi = 0이 됨. 대부분의 적용에서 하루는 한주기에 해당하며, ΔTi 는 고려된 기후에서 장비가 놓인 장소에서 보이는 밤과 낮의 온도 차이의 일일 평균에 해당.

프랑스의 기후는 ΔTi = 8 °C,

World-wide인 경우, ΔTi = 10 °C.

위 Table 3은 다음 사항이 고려되었다.

1) 장비의 3가지 내부 작동 온도를 고려하고 각 온도에 대한 연간 작동 시간을 고려. 전체 운용 시간을 500시간으로 산정함.

2) 아래와 같은 자동차의 열 순환을 고려함.

① Phase 1: 2 night starts

② Phase 2: 4 day light starts

③ Phase 3: non-used vehicle, dormant mode 30 days per year

위 Table 3을 보다시피 ISO 26262-11:2018 4.6.2.1.1 (IEC TR 62380:2004)에서 제시된 자동차에 대한 Mission profile에는 ‘Motor control’과 ‘Passenger compartment’라는 두 가지 파라메터들이 존재한다. 선택은 반도체가 적용될 위치에 따라 달라진다. ‘Motor control’은 차량의 엔진 룸 또는 Chassis 부분이며, ‘Passenger compartment’는 승객 룸을 포함하는 차량의 Body 부분이다. ‘Motor control’ 이 Passenger compartment’보다 환경 조건이 열악하기 때문에, 장착 위치와 상관없이 보수적으로 계산하기 위해서 ‘Motor control’을 선택할 수 있다. 다음은 ‘Passenger compartment’에서 사용되는 파라메터 값을 설명한다.

(tac)1 : 27 °C, 온도 사이클 3개 중 첫 번째 반도체 주변 PCB의 평균 주변 온도

τ1 : 0.006, 27 °C 에서 동작하는 시간의 연간 비율

(tac)2 : 30 °C, 온도 사이클 3개 중 두 번째 반도체 주변 PCB의 평균 주변 온도

τ2 : 0.046, 30 °C에서 동작하는 시간의 연간 비율

(tac)3 : 85 °C, 온도 사이클 3개 중 세 번째 반도체 주변 PCB의 평균 주변 온도

τ3 : 0.006, 85 °C에서 동작하는 시간의 연간 비율

τon : 0.058, 전원이 공급되어 동작하는 전체 시간의 연간 비율로서, τ1 + τ2 + τ3 = 0.006 + 0.046 + 0.006 = 0.058 또는 500 / (365x24) = 0.058이다.

τoff : 0.942, 동작하지 않거나 저장/휴면 모드 상태로 있는 전체 연간 시간 비율로서, 1 - τon = 1 - 0.058 = 0.942이다.

n1 : 670, 평균 온도 변동 ΔT1을 동반한 첫 번째 Phase에 일치하는 PCB의 컴포넌트에 의해 보이는 온도 사이클 수량(2 night starts)으로서, (365-30) x 2 = 670 cycles/year이다.

ΔT1 : 첫 번째 단계에서 PCB의 구성 요소에서 볼 수 있는 열 변동의 평균 편차.

(tac)1 working phases 동안의 평균 온도 : (0.006 x 27 + 0.046 x 30 + 0.006 x 85) / 0.058 = 35 °C

(tae)1 : night starts phase에서 장비(제어기)를 둘러싼 평균 외부 대기 온도, world wide night 평균 온도 5 °C 적용. (tac)1 - (tae)1 = 35 °C- 5 °C = 30 °C

n2 : 1340, 평균 온도 변동 ΔT2를 동반한 두 번째 Phase에 일치하는 PCB의 컴포넌트에 의해 보이는 온도 사이클 수량(4 day light starts)으로서, (365-30) x 4 = 1340 cycles/year이다.

ΔT2 : 두 번째 단계에서 PCB의 구성 요소에서 볼 수 있는 열 변동의 평균 편차

(tac)2 working phases 동안의 평균 온도 : (0.006 x 27 + 0.046 x 30 + 0.006 x 85) / 0.058 = 35 °C

(tae)2 : day light starts에서 장비(제어기)를 둘러싼 평균 외부 대기 온도, world wide day 평균온도 15 °C 적용. (tac)2 - (tae)2 = 35 °C – 15 °C = 20 °C

n3 : 30, 평균 온도 변동 ΔT3을 동반한 세 번째 Phase에 일치하는 PCB의 컴포넌트에 의해 보이는 온도 사이클 수량(non-used vehicle)으로서, 30 cycles/ year (dormant mode 30 days per year)이다.

ΔT3 : 세 번째 단계에서 PCB의 구성 요소에서 볼 수 있는 열 변동의 평균 편차.

Permanent working phase, storage or dormant에서는 장비가 본 사이클 당 최대 및 최소 온도 차이의 평균을 적용하기 위해 world wide ΔT3 = 10 °C 적용한다.

3.5 기본 고장률(BFR) 산정

1) 안전 메커니즘을 전혀 반영하지 않는 상태에서 반도체 엘리먼트에 대한 기본 고장률을 산정하기 위함이다.

기본 고장률에는 영구적인 것과 일시적인 것이 있으며, 서로 별도로 다루어지는 고장률이다. 다음은 이에 대한 작성 방안을 설명한다.

1) 영구적인 고장률(Permanent failure rate) 산정:

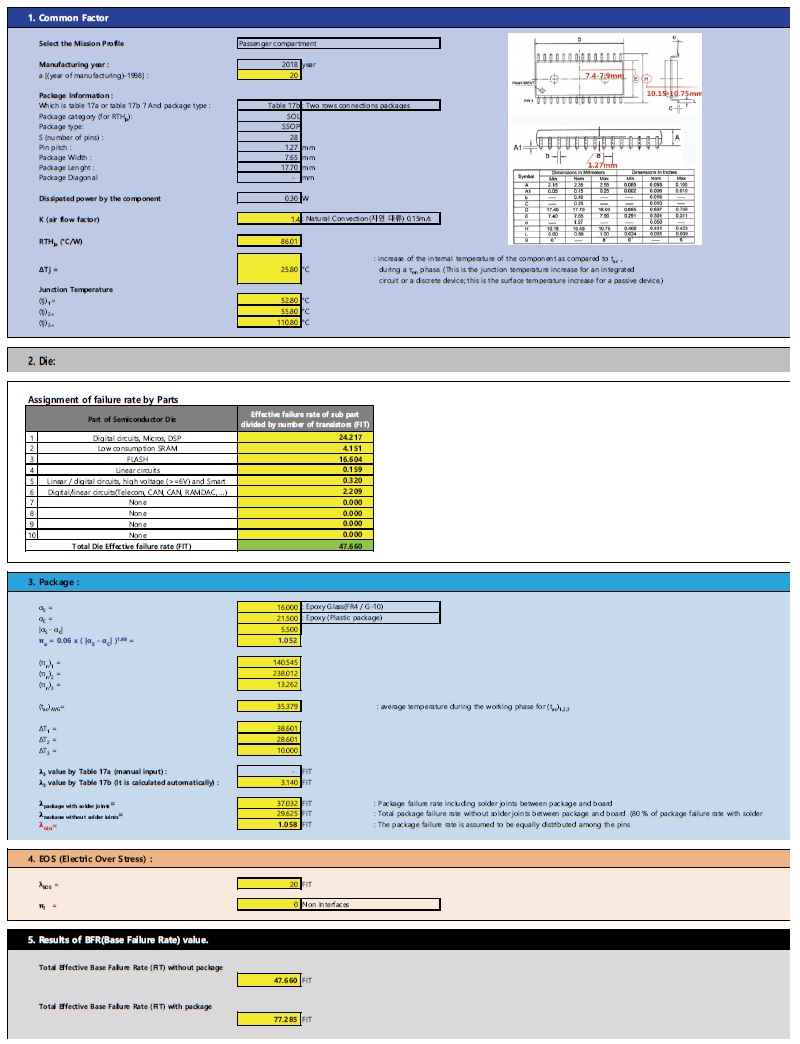

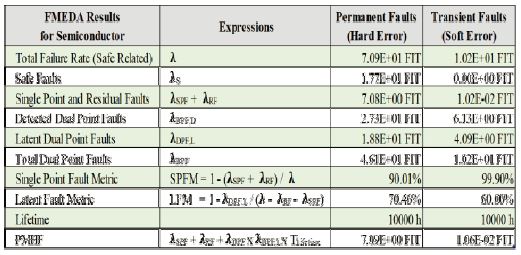

‘3.2 구조 분석’으로 부터 얻은 자료를 기반으로 반도체 엘리먼트에 대한 영구적인 고장률을 산정한다. Fig. 4는 엑셀 매크로를 활용한 반도체 엘리먼트에 대한 영구적인 고장률 산정을 보여준다. 참고로 “하드웨어 우발 고장 평가를 위한 기본 고장률 산정 및 고장 모드, 고장 모드 분포율 도출 방안”13)에서는 반도체 엘리먼트에 대한 영구적인 기본 고장률 계산에 대한 참고할 만한 정보를 제공해 준다. 다음은 Fig. 4에 대한 간략한 설명이다.

① Common factor:

-. Select the mission profile: ‘Motor control’ 또는 ‘Passenger compartment’ 둘 중 하나를 선택한다.

-. Manufacturing year: 반도체 제조 연도를 입력한다.

-. Package information: 반도체 Package에 대한 정보를 입력한다.

-. Dissipated power by the component: 반도체 소비 전력을 입력한다.

-. K(Air flow factor): 반도체 냉각 방식에 따라 선택된다. 이를 위해 IEC TR 62380 Table 13을 참조한다.

-. RTH ja (°C/W) : Thermal resistance between Junction and Ambient atmosphere. 수식에 의해 자동으로 계산된다.

-. ΔTj : 접합부 온도 증가. 수식에 의해 자동으로 계산된다.

② Die: 반도체 Die에 존재하는 반도체 엘리먼트별 고장률(Fit)이다.

③ Package: 반도체 Package에 대한 고장률(Fit)이다.

④ EOS: 반도체가 EOS에 노출될 경우 계산된다.

⑤ Result of BFR(Base Failure Rate) value: 반도체 Die와 package를 포함하는 반도체 기본 고장률 값이다.

2) 일시적인 고장률(Transient failure rate) 산정:

일시적인 결함은 영구적인 결함과는 달리 결함이 한번 발생하여 사라지는 결함으로써, 소프트 에러라고도 한다.2) 소프트 에러는 반도체 내부에서 알파선 혹은 중성자선 등에 의해 야기되는 전하에 의해 집적회로의 논리 노드 혹은 기억 노드의 신호 전위를 일시적으로 변동시키거나 반전시켜 발생하는 오류를 의미한다.2,14) 이러한 일시적인 고장률은 측정된 데이터로 지원되는 확률론적 방법으로만 정량화할 수 있는 우발 고장이다.2,14) 그러므로 일시적인 고장률은 반도체 웨이퍼 및 패키지에 중성자를 조사(照射)하여 측정된 데이터를 통해 얻게 된다.

1) 영구적인 고장률(Permanent failure rate)

Fig. 4는 IEC TR 623806)에 근거한 반도체의 영구적인 고장률 계산 예를 보여준다.

2) 일시적인 고장률(Transient failure rate)

메모리 및 디지털 파트에 대한 일시적인 고장률 값을 Foundry 업체로부터 얻는다. Table 4는 SRAM에 대한 일시적인 고장률 예를 보여준다. 사용 전압에 따라 Mbit 당 일시적인 고장률 값이 달라짐을 볼 수 있다.

3.6 기본 고장률 할당(BFR Allocation)

1) Die의 경우, 동일 유형을 가진 Part 단위의 고장률을 개별 하위 Sub-part 단위로 고장률을 분할하여 할당하기 위함이다.

2) Package의 경우, Pin 당 고장률을 적용하기 위함이다.

3.7 FMEDA 분석

1) 반도체 Sub part별로 안전 요구사항 위배 여부를 분석하여 단일점 결함(Single Point Fault), 잔존 결함(Residual Fault), 잠재 결함(Latent Fault)을 식별하기 위함이다.

2) 식별된 결함 유형을 바탕으로 반도체에 대한 HAM Hardware architecture metric)을 평가하기 위함이다.

3) 안전 요구 사항 위배에 대한 잔존 리스크가 충분히 낮은지를 평가하기 위함이다.

1) 반도체 아키텍처로부터 식별된 Sub part별로 단일점 결함(Single Point Fault), 잔존 결함(Residual Fault), 잠재 결함(Latent Fault)을 분류하여 영구적인 결함과 일시적인 결함에 대한 정량적 평가를 수행한다.

2) 기본 고장률 산정과는 달리 안전 메커니즘의 진단 커버리지를 반영하여 계산한다.

3) IP는 반도체의 Part 또는 Sub-part를 가리킨다.

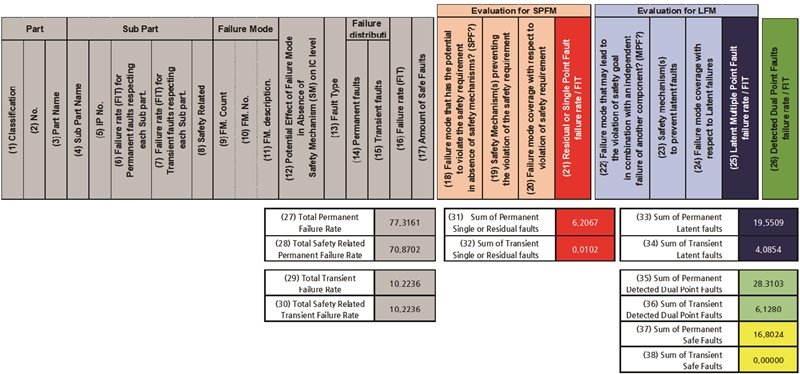

Fig. 5는 제안된 반도체 수준의 FMEDA 작성 양식이다. 아래는 이에 대한 설명이다.

1) Classification: Die part와 Package part를 구분

2) Part No: Semiconductor part number

3) Part Name: Semiconductor part name. ex) ADC, DAC, CPU, SPI, etc,..

4) Sub-part Name: Semiconductor sub-part name.

5) IP No: Semiconductor IP number

6) Failure rate(FIT) for Permanent faults respecting each Sub part: 기본 고장률 할당(BFR Allocation)으로부터 산출된 각 IP 별 영구 결함률을 기입.

7) Failure rate(FIT) for Transient faults respecting each Sub part: 기본 고장률 할당(BFR Allocation)으로부터 산출된 각 IP 별 일시적 결함률을 기입. 만약, 특정 IP에 대하여 일시적 결함을 구하지 않는 경우라면, ‘0’으로 기입한다.

8) Safety Related: IP가 안전 관련인지에 대한 여부를 ‘SR(Safety Related)’ 또는 ‘NSR(No Safety Relate)’ 택일하여 기입한다.

9) FM. Count: 기술된 고장 모드(Failure mode)에 대한 개수. 일반적으로 고장률 분포를 균등 분할하기 위해 사용된다.

10) FM. No: 고장 모드(Failure mode) 번호

11) FM. Description: FMEA, FTA, DFA와 같은 안전 분석에 의해 식별된 각 IP 별 고장 모드를 기술한다.

12) Potential Effect of Failure Mode in Absence of Safety Mechanism(SM) on IC level: 안전 메커니즘 부재 시, 각 고장 모드로 초래될 수 있는 영향을 기술한다. 주의할 점은, 해당 IP를 방어할 수 있는 안전 메커니즘이 실제로 있더라도 이를 무시해야 한다.

13) Fault Type: 고장의 형태를 영구결함 또는 일시적인 결함으로 분류한다. ‘P’(Permanent) 또는 ‘T’(Transient) 둘 중 하나 택일하여 기입한다.

14) (Failure distribution for) Permanent faults: 영구적인 결함에 대한 고장모드 분포율을 할당한다.

15) (Failure distribution for) Transient faults: 일시적인 결함에 대한 고장모드 분포율을 할당한다.

16) Failure rate (FIT): 식별된 IP에 대한 고장 모드별로 고장률을 계산한다.

a. 13) Fault Type이 ‘P’일 경우: IP 영구적인 고장률 × 영구적인 고장 모드 분포율

b. 13) Fault Type이 ‘T’일 경우: IP 일시적인 고장률 × 일시적인 고장 모드 분포율

17) Amount of Safe Faults: IP 고장 모드별로 안전 결함(Safe Fault)의 비율을 반영한다.

18) Failure mode that has the potential to violate the safety requirement in absence of safety mechanisms? (SPF?): IP에 대한 고장 모드별로 안전 메커니즘이 부재 시 단일점 결함을 초래하는지 판단한다. 주의할 점으로 해당 IP를 방어할 수 있는 안전 메커니즘이 실제로 있더라도 이를 무시해야 한다.

19) Safety Mechanism(s) preventing the violation of the safety requirement: 18)번에서 ‘Y’를 선택한 경우, 이를 방지할 수 있는 안전 메커니즘이 있다면 안전메커니즘의 ID를 기입한다. 만약 ‘N’을 선택했다면, 공란으로 비워 둔다.

20) Failure mode coverage with respect to violation of safety requirement: 19)번에 적용된 안전 메커니즘의 진단 커버리지 값을 기입한다. 만약 19)번에 적용된 안전 메커니즘이 없다면 공란으로 비워 둔다.

21) Residual or Single point fault failure rate / FIT: 단일점 결함(Single point fault) 또는 잔존 결함(Residual fault)의 고장률을 자동으로 계산한다.

22) Failure mode that may lead to the violation of safety goal in combination with an independent failure of another component? (MPF?): 다른 독립적인 결함과 결합하여 안전목표 (안전요구사항)을 위배하는 결함인지를 판단한다.

23) Safety mechanism(s) to prevent latent faults: 22)번에서 ‘Y’를 선택한 경우, 이를 방지할 수 있는 안전 메커니즘이 있다면 안전메커니즘의 ID를 기입한다. 만약 ‘N’을 선택했다면, 공란으로 비워 둔다.

24) Failure mode coverage with respect to latent failures: 23)번에 적용된 안전 메커니즘의 진단 커버리지 값을 기입한다. 만약 23)번에 적용된 안전 메커니즘이 없다면 공란으로 비워 둔다.

25) Latent multiple point fault failure rate / FIT: 22)번이 ‘Y’라면, 다중점 잠재 결함률(Latent Failure Rate)을 자동으로 계산한다.

26) Detected dual point faults failure rate / FIT: 22)번이 ‘Y’’라면, 감지된 이중점 결함률(Detected dual point faults failure rate)을 자동으로 계산한다.

27) Total Permanent Failure Rate: 영구적인 고장률에 대한 총 합계 값이다.

28) Total safety related permanent failure rate: 안전 관련 고장률 중에서 영구적인 고장률에 대한 총 합계 값이다.

29) Total transient failure rate: 일시적인 고장률에 대한 총 합계 값이다.

30) Total Safety Related Transient Failure Rate: 안전 관련 고장률 중에서 일시적인 고장률에 대한 총 합계 값이다.

31) Sum of permanent single or residual faults: 영구적인 고장률 중에서 단일점 결함률과 잔존 결함률을 합산한 값이다.

32) Sum of transient single or residual faults: 일시적인 고장률 중에서 단일점 결함률과 잔존 결함률을 합산한 값이다.

33) Sum of permanent latent faults: 영구적인 고장률 중에서 잠재 결함률의 총 합계 값이다.

34) Sum of transient latent faults: 일시적인 고장률 중에서 잠재 결함률의 총 합계 값이다.

35) Sum of permanent detected dual point faults: 영구적인 고장률 중에서 감지된 이중점 결함률을 합산한 값이다.

36) Sum of transient detected dual point faults: 일시적인 고장률 중에서 감지된 이중점 결함률을 합산한 값이다.

37) Sum of prmanent safe faults: 영구적인 고장률에서의 안전측 결함의 총합이다.

38) Sum of transient safe faults: 일시적인 고장률에서의 안전측 결함의 총합이다.

4. 결 론

기능안전 ISO 26262:2018에서 요구되는 설계 기법 및 절차들은 기존 반도체 산업에 있어 상당히 낯선 것이 현실이다. 이 중에서도 특히 정량적 평가의 경우가 더욱 그러한데, 불행히도 반도체 수준의 정량적 평가와 관련하여 참고할 만한 문서는 더욱 찾아보기 힘들다. 이에 본문에서는 정량적 평가에서 사용되는 FMEDA 기법을 반도체 수준에 맞춰 소개하였고, 이에 대한 작성 절차를 제시하였다. 제시된 반도체 수준의 FMEDA 작성 방안을 참고한다면, 기능안전 ISO 26262-5:20184)에서 요구되는 정량적 평가 수행을 반도체 수준에 맞춰 진행할 수 있을 것으로 기대한다.

Nomenclature

| ADS : | automated driving system |

| ASIL : | automotive safety integrity level |

| BFR : | base failure rate |

| DC : | diagnostic coverage |

| E/E System : | electric/electronic system |

| EOS : | electric over stress |

| FIT : | failure in time |

| FMEDA : | failure modes effects and diagnostics analysis |

| FSR : | functional safety requirement |

| HW : | hardware |

| IP : | intellectual property |

| SG : | safety goal |

| SPI : | serial peripheral interface |

| SW : | software |

| TSR : | technical safety requirement |

Acknowledgments

본 문에서는 반도체 수준의 FMEDA 작성 방안 및 절차를 소개하였으나, 정작 반도체 Die와 Package에 대한 FMEDA 분석 내용은 보여주지 못했다. 그렇기 때문에 향후 과제로서 실무에 적용할 수 있는 반도체 FMEDA 분석 사례에 대한 연구가 필요해 보인다.

References

- U. S. Department of Transportation, NHTSA (National Highway Traffic Safety Administration), A Framework for Automated Driving System Testable Cases and Scenarios, September 2018.

- ISO 26262-11:2018, Road Vehicles Functional Safety Part 11: Guidelines on Application of ISO 26262 to Semiconductors, 2nd Edn., 2018.

- ISO 26262-4:2018, Road Vehicles Functional Safety Part 4: Product Development at the System Level, 2nd Edn., 2018.

- ISO 26262-5:2018, Road Vehicles Functional Safety Part 5: Product Development at the Hardware Level, 2nd Edn., 2018.

- ISO 26262-6:2018, Road Vehicles Functional Safety Part 6: Product Development at the Software Level, 2nd Edn., 2018.

- International Electrotechnical Commission, IEC TR 62380 Edition 1.0: Reliability Data Handbook - Universal Model for Reliability Prediction of Electronics Components, PCBs and Equipment, IEC, 2004.

- ISO 26262-10:2011, Road Vehicles Functional Safety Part 10: Guideline on ISO 26262, 1st Edn., 2011.

- ISO 26262-10:2018, Road Vehicles Functional Safety Part 10: Guideline on ISO 26262, 2nd Edn., 2018.

- KS R ISO 26262:2011, Road Vehicles - Functional Safety - Part 1: Vocabulary, 2012.

-

B. K. Park and S. H. Lee, “The Methods for Describe the Safety Mechanism and Estimate the Diagnostic Coverage in order to Conduct the Eficient FMEDA,” Transactions of KSAE, Vol.26, pp.791-798, 2018.

[https://doi.org/10.7467/KSAE.2018.26.6.791]

- IEC 61709, Electronic Components - Reliability - Reference Conditions for Failure Rates and Stress Models for Conversion, Edition 3.0, 2017.02.

- FIDES Guide 2009 Edition A, Reliability Methodology for Electronic Systems, 2010.

-

B. K. Park and S. H. Lee, “The Method for Estimate of Basic Failure Rate and Derivation of Failure Mode and Failure Mode Distribution Rate in order to Evaluate of Random Hardware Failure,” Transactions of KSAE, Vol.28, No.8, pp.551-561, 2020.

[https://doi.org/10.7467/KSAE.2020.28.8.551]

- JEDEC JESD89A, Measurement and Reporting of Alpha Particle and Terrestrial Cosmic Ray-Induced Soft Errors in Semiconductor Devices, 2006.