MOSFET 소자 수 저감이 가능한 단일 전력단 OBC

Copyright Ⓒ 2026 KSAE / 242-05

This is an Open-Access article distributed under the terms of the eative Commons Attribution Non-Commercial License(http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium provided the original work is properly cited.

Abstract

This paper proposes a single-stage on-board charger designed to reduce the number of MOSFET devices used. It integrates an inverter power factor correction circuit utilizing unipolar pulse width modulation and a half-bridge LLC resonant converter. The entire circuit consists of four wide bandgap power semiconductor devices. The analytical formulation of the zero voltage switching turn-on condition for the integrated switching leg is provided, accompanied by a design methodology rooted in detailed analysis. The effectiveness of the proposed switching method is demonstrated through experimental results from a prototype circuit with a 220 Vac 50 Hz input / 400~800 VDC 3.7 kW output.

Keywords:

Electric vehicle, On-board charger, Power factor correction, Resonant converter, Zero voltage switching키워드:

전기 자동차, 차량 탑재형 충전기, 역률 개선, 공진형 컨버터, 영전압 스위칭1. 서 론

OBC는 EV내에 탑재된 여러 전력변환장치 중의 하나로, HV 배터리의 충전을 담당한다.1) OBC에서 가공 및 처리하는 전력 용량이 커질수록 HV 배터리 충전 속도는 빨라지나, OBC의 전력 용량 상승은 회로를 구성하는 반도체 소자 수의 증가나 수동 소자 부피 증가 등의 문제를 야기한다. 하지만, OBC는 주로 차량의 남는 공간에 위치하기에 회로 부피를 최소화하는 고밀도 설계가 필수적이다.2,3)

고밀도 OBC 설계를 위해 여러 연구들이 수행된 바 있으며, WBG 소자를 적용한 OBC 개발이 대표적인 예시이다.4) WBG 소자의 적용은 OBC의 출력 전압을 높여 전력용량 상승을 달성했을 뿐 아니라, WBG 소자의 스위칭 특성을 바탕으로 회로를 구성하는 주요 Topology들의 동작 주파수 상승과 수동 소자 및 전체 회로의 부피 저감을 이룩하였다.5,6) 그러나, 이와 같은 기술적 진보는 반도체 소자의 기술 발전에 기인한 것이지, OBC를 구성하는 Topology들의 구조적 개선이나 제어 기법 개선과는 거리가 멀다는 점에서 한계점이 존재한다. 따라서, 부피 저감을 통한 고밀도 OBC 개발을 위해서는 회로 구조적 접근을 바탕으로 하는 연구가 필요하다.

회로 구조를 다룬 대표적인 OBC 연구로는 비절연 OBC와 단일 전력단 OBC가 있다. 비절연 OBC는 DC/DC 컨버터의 고주파 변압기를 제거한 OBC로, 자성체 소자가 생략된 만큼 회로 부피를 줄일 수 있는 이점이 있다. 그러나, 고주파 변압기의 제거로 인해, CMI와 CMV 등의 EMI 문제가 크게 발생하므로, 복잡한 제어 방안이나 별도의 회로 구조가 필요하다는 단점이 있다. 특히, CMI는 인체 감전과 직결되므로 안전성 측면에서 실제 적용이 까다롭다는 부가적인 문제도 존재한다.

단일 전력단 OBC는 PFC와 DC/DC 컨버터의 통합 구조를 갖는 OBC이다. 절연형 DC/DC 컨버터를 적용하고 주요 소자를 통합한 구조를 갖는다면, EMI 및 인체 감전 문제의 해소와 더불어 소자 수 저감, 전력 밀도 상승, 안전성 등의 장점을 부각할 수 있다. 이러한 점에서 단일 전력단 OBC는 연구 가치가 높다.

단일 전력단 OBC를 다룬 여러 연구 결과들이 보고된 바 있다. Interleaved Cascade Buck-Boost 구조를 활용한 OBC나,7) PFC단 링크 커패시터를 제거한 단일 전력단 구조,8~10) Current Source 방식을 활용한 OBC,11) 직렬 공진 방식을 활용한 Active Clamp Forward 컨버터의 모듈형 구조12) 등이 그 예시이다. 그러나 위와 같은 기존 연구 성과들은 교류 입력 전압 측의 다이오드 정류기로 인해 불필요한 전력 손실이 발생하고,7,11) 회로를 구성하는 Mosfet 소자 수가 많거나 출력 전류의 저주파 변동이 크게 발생하는 단점들이 존재한다.8-11) OBC의 부피저감과 EV의 상품성 개선 및 경쟁력 고취를 위해서는 상술한 단점들을 해소할 수 있는 단일 전력단 OBC 구조가 필요하다.

본 논문에서는 스위치 레그를 공유하는 단일 전력단 OBC와 ZVS 조건 분석, 이를 고려한 설계 방안을 소개한다. 제안하는 회로는 Inverter PFC와 Half-Bridge LLC 공진형 컨버터를 Single-Stage로 통합한 구조로, 회로 내에 존재하는 MOSFET 소자 수는 4개에 불과하여 소자 수 저감과 고밀도 OBC 설계가 가능하다. 제안하는 단일 전력단 OBC의 유효성은 220 Vac 50 Hz input / 3.7 kW 400 ~ 800 VDC output 실험으로 검증하였다.

2. 제안하는 회로 구조와 PWM 방안

2.1 스위치를 통합한 단일 전력단 OBC 회로 구조

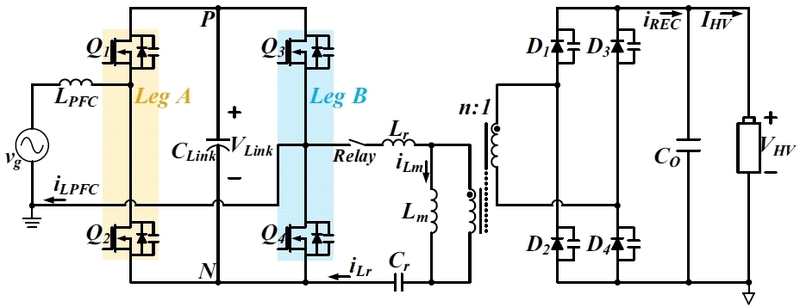

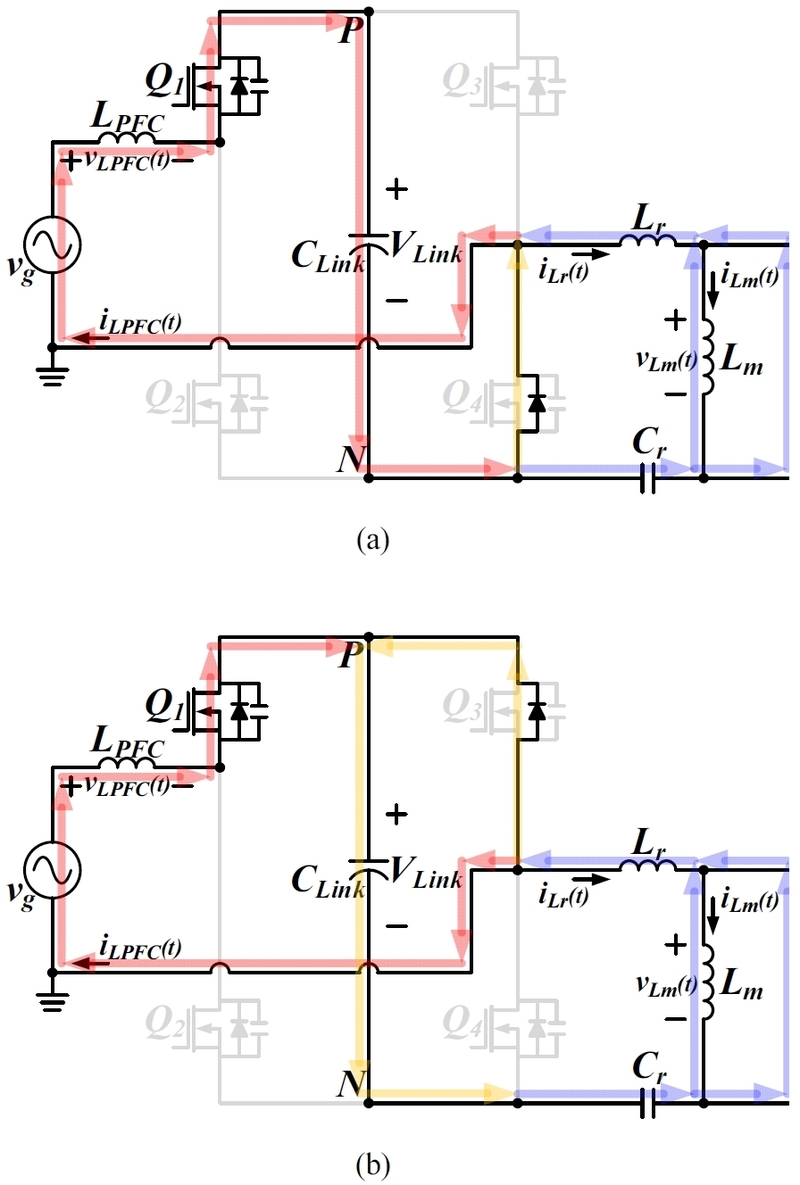

Fig. 1은 제안하는 단일 전력단 OBC의 회로 구조를 나타낸다. 제안하는 OBC의 1차측 회로에서 PFC 인덕터 LPFC, Q1 ~ Q4로 구성되는 두 개의 스위칭 레그 Leg A & B, 링크 커패시터 CLink는 PFC 동작을 수행한다. 또한, Leg B는 릴레이, 공진 커패시터 Cr, 공진 인덕터 Lr, 변압기 및 자화 인덕턴스 Lm을 포함하여 Half-Bridge LLC 공진형 컨버터의 1차측 회로를 구성한다. 여기서, 릴레이는 CLink의 초기 충전 및 VLink가 Half-Bridge LLC 공진형 컨버터의 정격 입력 전압까지 도달하기 이전에는 항상 개방 상태를 유지하며, Half-Bridge LLC 공진형 컨버터가 전력 전달을 수행하는 순간부터 단락 상태로 전환된다.

2차측 회로는 D1 ~ D4로 구성되는 Full-Bridge 정류부, LLC 출력 커패시터 CO 그리고 부하로 구성되는 일반적인 LLC 공진형 컨버터의 2차측 구조와 동일하다.

제안하는 회로의 1차측 스위칭 레그 중에서, Leg B는 PFC 동작과 LLC 공진형 컨버터의 동작을 겸한다. 이러한 점에서 제안하는 회로는 단일 전력단 구조라고 할 수 있다.

2.2 제안 회로의 동작 방식

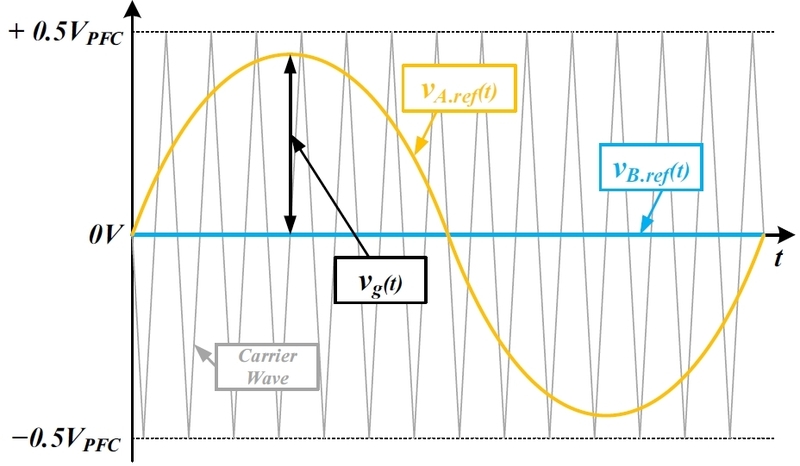

서론에서 서술한 바와 같이, 제안하는 단일 전력단 OBC에는 Inverter PFC를 적용한다. 다시 말해, Leg A와 Leg B 모두 고속 스위칭 동작을 수행한다. Fig. 2는 교류 입력 전압에 따른 제안하는 단일 전력단 OBC의 PFC 동작 개념 및 극전압 지령 파형을 보여준다.

Leg B가 Half-Bridge LLC 공진형 컨버터의 1차측 스위치 레그로 동작하기 위해서 Leg B는 0.5 고정 시비율로 동작해야 하며, 이는 Leg B의 극전압 지령 vB.ref(t)가 0 V라는 것과 같다. 이 때, 인버터의 기본 동작 원리에 따라, Leg A와 Leg B의 극전압 차이는 입력 교류 전압과 동일해야 하므로, Leg A의 극전압 지령 vA.ref(t)는 입력 교류 전압 vg(t)와 동일하다.

위와 같은 두 레그의 극전압 지령을 토대로, Leg A와 Leg B를 구성하는 스위치 Q1 ~ Q4의 시비율 DQ1(t) ~ DQ4(t) 는 아래의 식 (1)과 같이 표현된다.

| (1) |

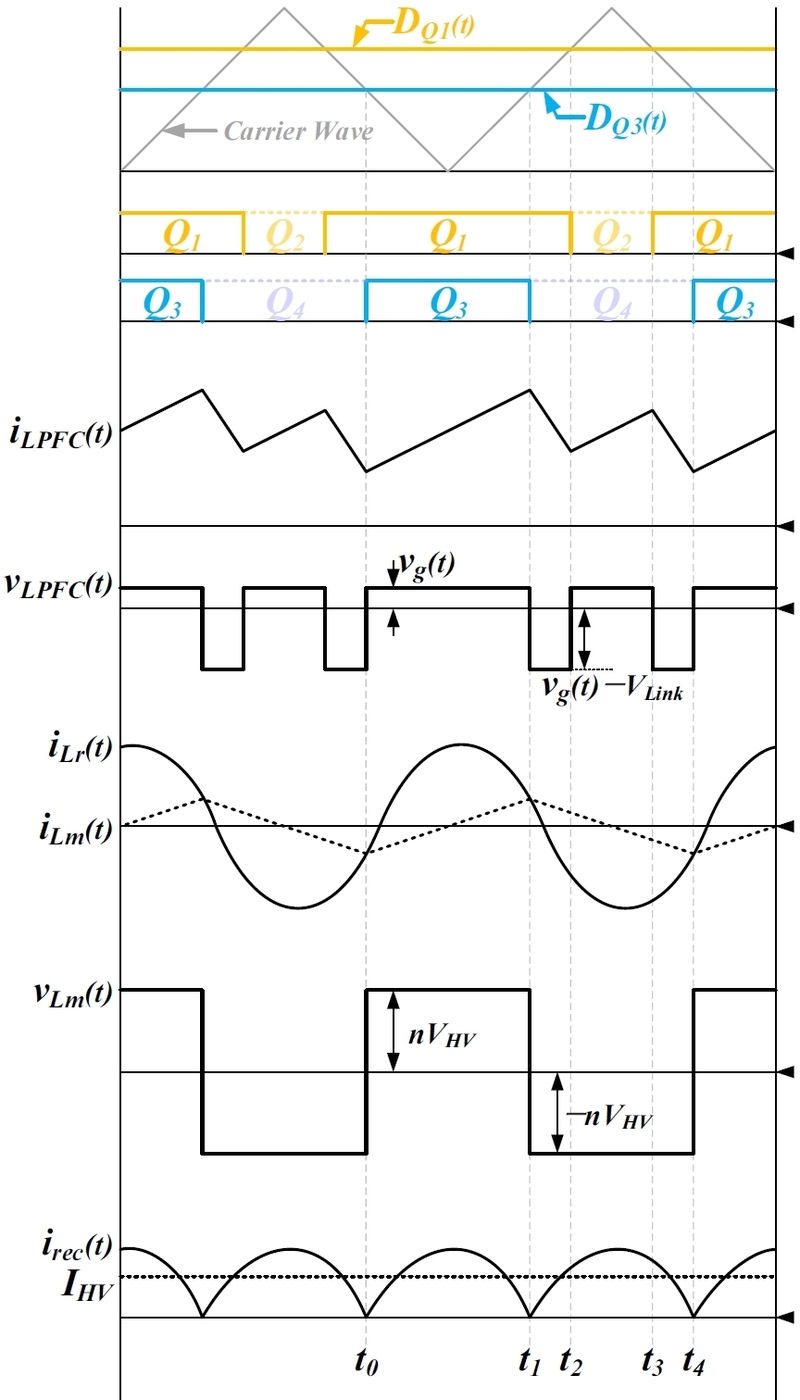

Fig. 3은 입력 교류 전압 vg(t)의 양의 반주기 한 지점에서 제안하는 단일 전력단 OBC의 게이트 시그널, LPFC 양단 전압 vLPFC(t), PFC 인덕터 전류 iLPFC(t), Half-Bridge LLC 공진형 컨버터의 1차측 공진 전류 iLr(t)를 나타낸다.

제안하는 단일 전력단 OBC의 동작 분석은 아래의 Mode 1 ~ 4와 같다. 설명의 편의를 위해, PFC 링크 전압 VLink는 항상 일정하고, 제안하는 회로가 Half-Bridge LLC 공진형 컨버터의 공진 주파수로 동작한다고 가정하며, 데드 타임은 무시하였다. 또한, Half-Bridge LLC 공진형 컨버터의 릴레이가 단락되어, HV 배터리측으로 전력이 전달되고 있는 상황을 가정한다.

Mode 1 [t0 ~ t1] : Q1과 Q3가 턴 온된 상태로, LPFC에 vg(t)가 인가되어 iLPFC(t)가 증가한다. iLPFC(t)의 증가는 Q3가 턴 오프될 때까지 지속된다. 공진 전류 iLr(t)은 양의 정현파 형태로 변화하며 변압기를 통해 2차측으로 전달된다. 2차측 다이오드 정류기의 D1과 D3가 순방향 바이어스됨에 따라, Lm에는 nVHV가 인가되어 iLm(t)가 증가한다.

Mode 2 [t1 ~ t2] : Q1과 Q4가 턴 온된 상태로, LPFC에 vg(t)−VLink가 인가되어 iLPFC(t)가 감소한다. iLPFC(t)의 감소는 Q1이 턴 오프될 때까지 지속된다. 공진 전류 iLr(t)은 양의 정현파 형태에서 음의 정현파 형태로 변화하며 변압기를 통해 2차측으로 전달된다. 2차측 다이오드 정류기의 D2와 D4가 순방향 바이어스됨에 따라, Lm에는 −nVHV가 인가되어 iLm(t)가 감소한다.

Mode 3 [t2 ~ t3] : Q2와 Q4가 턴 온된 상태로, LPFC에 vg(t)가 인가되어 iLPFC(t)가 증가한다. iLPFC(t)의 증가는 Q2가 턴 오프될 때까지 지속된다. 공진 전류 iLr(t)은 음의 정현파 형태로 변화하며 변압기를 통해 2차측으로 전달된다. 앞선 Mode 2와 마찬가지로 2차측 다이오드 정류기의 D2와 D4가 순방향 바이어스됨에 따라, Lm에는 −nVHV가 인가되어 iLm(t)가 감소한다.

Mode 4 [t3 ~ t4] : Q1와 Q4가 턴 온된 상태로, 전체적인 동작이 Mode 2와 유사하다. LPFC에 vg(t)−VLink가 인가되어 iLPFC(t)가 감소한다. iLPFC(t)의 감소는 Q4가 턴 오프될 때까지 지속된다. 공진 전류 iLr(t)은 음의 정현파 형태로 변화하며 변압기를 통해 2차측으로 전달된다. 앞선 Mode 3와 마찬가지로 2차측 다이오드 정류기의 D2와 D4가 순방향 바이어스되어 있으며, 이에 따라 Lm에는 −nVHV가 인가되고 iLm(t)가 감소한다.

Fig. 3 및 상기 Mode 1 ~ 4의 동작 분석을 바탕으로, 제안하는 단일 전력단 OBC의 PFC 인덕터 전류의 최대 전류 리플은 입력 전압 양의 반주기를 기준으로 Q3가 턴 온되는 구간에서 발생함을 알 수 있다. Q3는 한 번의 스위칭 주기 Ts에서 0.5 고정 시비율로 턴 온 되므로, 제안 회로의 스위칭 주파수를 fs라 할 때, LPFC의 전류 리플은 아래의 식 (2)와 같이 표현되며, t0 및 t4 시점에서의 PFC 인덕터 전류는 식 (3)과 같이 계산된다.

| (2) |

| (3) |

여기서, PO는 제안 회로의 출력 전력, vg.rms는 vg(t)의 실효값을 의미한다.

3. 제안 회로의 ZVS 조건 분석

일반적으로, Unipolar PWM 방식을 사용하는 단상 PFC에서 입력 교류 전압 양의 반주기 동안에는 Q2와 Q3가, 음의 반주기 동안에는 Q1과 Q4가 하드 스위칭 턴 온 된다. 그러나, 제안하는 단일 전력단 OBC는 Q3와 Q4가 Half-Bridge LLC 공진형 컨버터의 1차측 회로 역할을 겸하기 때문에 PFC 인덕터 전류 iLPFC(t)가 작은 값을 갖는 구간에서 ZVS 턴 온이 달성되는 Partial ZVS 턴 온 특징이 존재한다. Partial ZVS 턴 온은 iLPFC(t)와 공진 인덕터 전류 iLr(t) 및 주요 소자들에 의해 결정되며, 본 절에서는 Leg B의 Partial ZVS 턴 온 성취 조건에 대한 분석을 진행한다. 상세한 분석 및 동작 상황은 입력 교류 전압 vg(t)가 양의 반주기 한 지점이고, VLink는 일정하며, 제안하는 회로가 공진 주파수로 동작함을 가정한다.

3.1 ZVS 턴온 성취를 위한 기본 개념

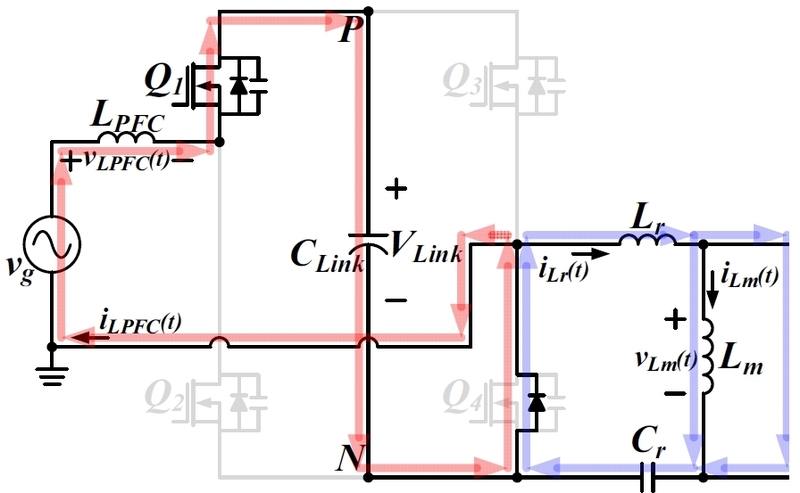

Fig. 3의 t1 시점(Mode 1에서 Mode 2로 전환되는 구간)에서는 iLPFC(t1)와 iLr(t1) 모두 양의 값을 가지므로 Fig. 4와 같이 Q4가 턴 온되기 이전에 Q4의 기생 커패시턴스 방전과 역병렬 다이오드의 도통이 이루어진다. 따라서, 양의 반주기동안 Q4의 ZVS 턴 온은 원활히 이루어진다.

반면, Fig. 3의 t4(또는 t0) 시점(Mode 4에서 Mode 0로 전환되는 구간)에서 iLPFC(t4)는 양의 값을 가지나 iLr(t4)는 음의 값을 가지므로 iLPFC(t4)와 |iLr(t4)|의 대소관계, Lr과 Q3의 기생 커패시턴스에 저장된 에너지 크기에 따라 Q3의 ZVS 턴 온 성취 여부가 달라진다.

iLPFC(t4)가 |iLr(t4)|보다 크면, Fig. 5(a)와 같이 두 전류 값의 차이에 해당하는 전류가 Q4의 턴 오프 이후, Q4의 역병렬 다이오드를 따라 흐른다. 이 경우, Q3의 ZVS 턴 온은 불가능하다.

The current flow of the proposed OBC prior to Q3 turn-on. (a) iLPFC(t4) > |iLr(t4)|. (b) |iLr(t4)| > iLPFC(t4)

이와 반대로, |iLr(t4)|가 iLPFC(t4)보다 크고 Lr이 가지는 에너지가 Q3의 기생 커패시턴스에 저장된 에너지보다 크면, Fig. 5(b)와 같이 두 전류 값의 차이에 해당하는 전류가 Q3의 기생 커패시턴스를 방전한 후 Q3의 역병렬 다이오드를 따라 흐른다. 이후 Q3의 ZVS 턴온이 달성되며, 이와 같은 상관관계를 바탕으로 입력 교류 전압 vg(t) 양의 반주기에서 Q3의 ZVS 턴 온 달성을 위해서는 아래의 식 (4)가 만족되어야 한다.

| (4) |

여기서, COSS는 Q3와 Q4의 기생 커패시턴스를 의미한다.

3.2 ZVS 턴온 성취를 위한 수식 분석

상술한 바와 같이 Q3의 ZVS 턴 온은 |iLr(t4)|와 iLPFC(t4)의 대소관계가 주요한 요소인데, iLPFC(t4)는 PFC 동작에 의해 지속적으로 변하는 값이므로, Partial ZVS 턴 온 달성 구간 설정을 위해 iLPFC(t4) 값을 특정할 필요가 있다. 특정된 iLPFC(t4)를 iLPFC.ZVS 라고 하고, iLr(t4)가 음의 값을 가짐을 고려하면, 식 (4)는 식 (5)와 같이 표현 가능하다.

| (5) |

앞서, 제안하는 회로의 동작 주파수가 공진 주파수와 동일하다고 가정하였으므로 iLr(t4)는 iLm(t4)와 같다. 또한, Half-Bridge LLC 공진형 컨버터의 공진 주파수 동작에서 입출력 전압 이득 M은 식 (6)과 같으므로, 식 (5)는 다음의 식 (7)과 같이 다시 표현될 수 있다.

| (6) |

| (7) |

여기서, 식 (6)의 fS는 스위칭 주파수, fr은 공진 주파수를 의미한다. 한편, 식 (8)과 같이 Lr에 대한 Lm의 비율을 k라고 하고, 식 (8)을 식 (7)에 대입하여 k에 대해 정리하면 식 (9)와 같이 나타난다.

| (8) |

| (9) |

식 (9)에서, 설계자가 원하는 MOSFET 소자를 선정하고, 시스템 사양에 맞게끔 VLink, fr, iLPFC.ZVS를 설정한 후, 적절한 수준의 Lm을 선정한다면, 제안하는 단일 전력단 OBC의 Partial ZVS 턴온 성취를 위한 k의 범위를 도출 및 공진 인덕턴스 Lr을 설계할 수 있다.

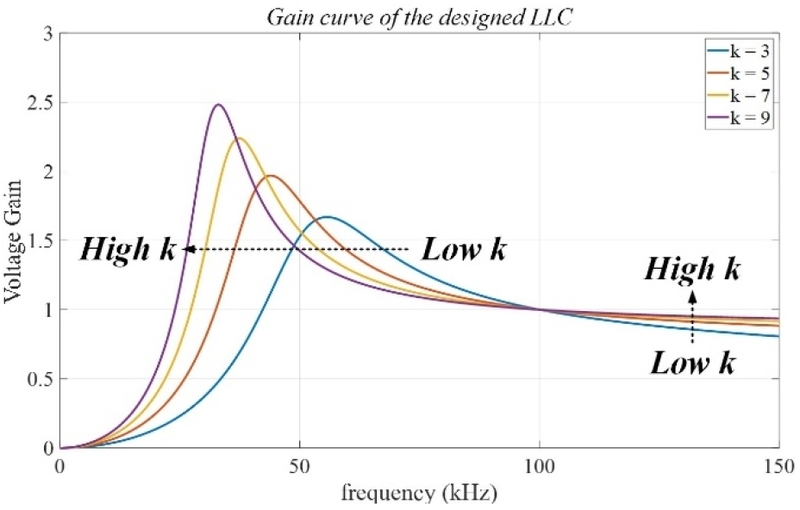

Partial ZVS 턴온 범위는 식 (9)를 통해 설계자가 원하는 수준까지 달성할 수 있다. 그러나, Half-Bridge LLC 공진형 컨버터는 공진 네트워크의 파라미터에 따라 전압 이득이 달라지므로, 식 (9)에 더하여 원하는 전압 이득 확보가 가능한 공진 네트워크의 파라미터 선정이 필요하다. Fig. 6은 Table 1의 파라미터를 적용할 때, k에 따른 Half‑Bridge LLC 공진형 컨버터의 전압 이득 곡선을 보여준다. Fig. 7을 통해 Lm이 동일할 때, k가 큰 값을 가질수록 원하는 전압 이득 확보를 위한 Below 영역의 최저 동작 주파수가 작아지는 양상을 확인할 수 있다. 이러한 결과와 식 (9)를 미루어 볼 때, 적절한 Lm을 선정하더라도 식 (9)에 의해 계산되는 최대 k를 적용하면 동작 주파수 범위가 과도하게 확장되므로 이를 제한하기 위해 최대 k보다 작은 값의 k를 선정하는 것이 Partial ZVS 턴온과 동작 주파수 범위의 최소화 모두 달성 가능함을 알 수 있다.

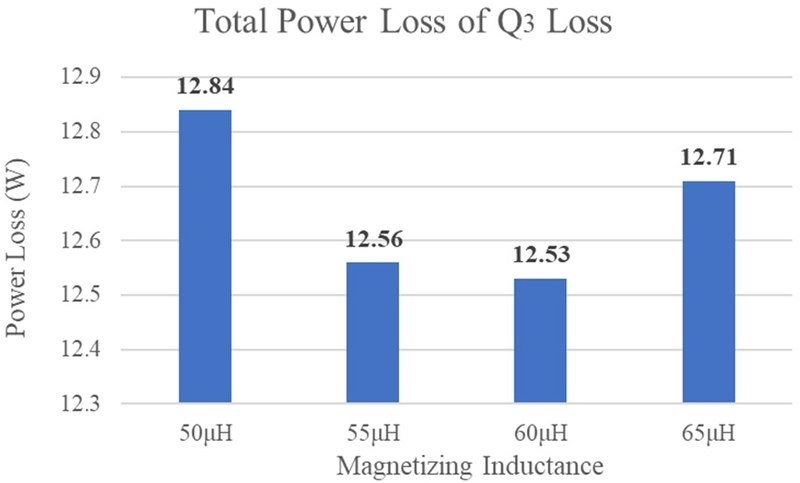

한편, Lm을 작게 설계하는 것은 Partial ZVS 범위를 넓힐 수는 있으나, 큰 자화 전류 리플로 인한 스위치 소자의 높은 턴 오프 손실을 유발한다. 또한, 과도하게 큰 Lm은 Partial ZVS 범위를 축소시켜 보다 큰 턴온 손실을 유발한다. 따라서, Lm은 입출력 사양과 스위치 소자에서 발생하는 전력 손실을 종합적으로 고려하여 선정되어야 한다. Fig. 7은 Table 1의 파라미터 중에서 Lm을 50 ~ 65 μH로 가변하고 k는 4로 고정할때, Q3의 총 전력 손실을 보여준다. 그래프에서 확인할 수 있듯이, Lm이 50 μH인 경우와 65μH인 경우에 총 전력 손실이 크게 나타났으며, 50 μH에서는 턴 오프 손실로 인해 총 전력 손실이 상대적으로 크게 나타났으며, 반대로 65 μH에서는 Partial ZVS 범위 축소로 인한 턴온 손실로 인해 총 전력 손실이 크게 발생하였다. 따라서, 제안하는 단일 전력단 OBC는 턴온 손실과 턴오프 손실을 종합적으로 고려하여 총 손실이 최소화가 되는 Lm을 선정하는 것이 중요하다.

4. 실험을 통한 제안 회로의 유효성 검증

4.1 실험 사양 및 주요 설계 파라미터

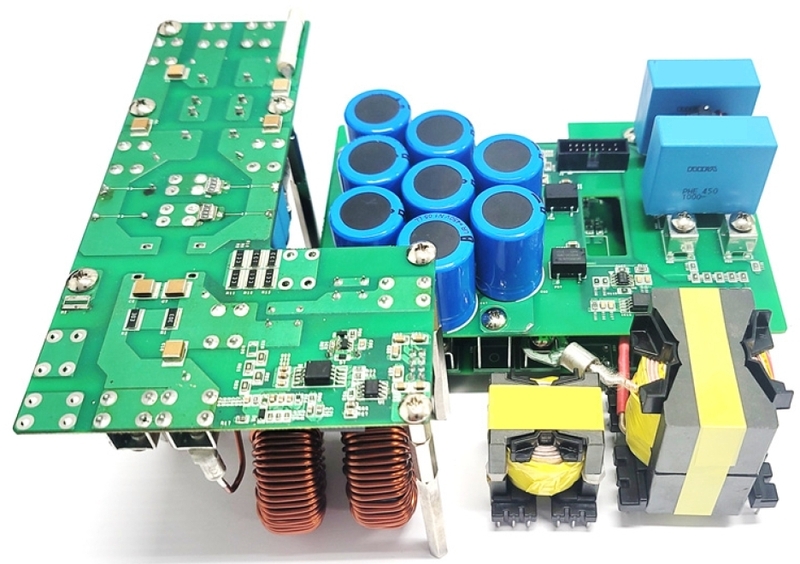

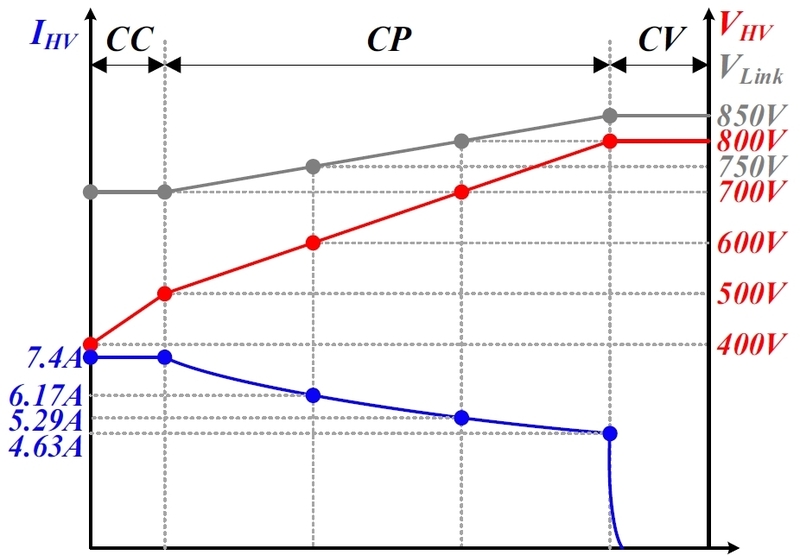

제안하는 단일 전력단 OBC의 유효성을 검증하기 위해 Fig. 8과 같은 Prototype 회로를 설계하여 실험을 진행하였다. 설계에 앞서, OBC의 배터리 충전 프로파일을 Fig. 9와 같이 설정하였다. OBC 출력 전압 VHV의 400 ~ 500 V 구간은 CC 동작, 500 ~ 800 V구간은 CP로 가정하였고, 주요 입출력 사양은 Table 2에 정리된 바와 같다. High Flux Toroid를 적용한 PFC 인덕터의 투자율 변화에 따른 인덕턴스 변화를 고려하여, iLPFC.ZVS는 약 8.95 A로설정하였다.

Half-Bridge LLC의 공진 탱크소자 파라미터는 식 (8)과 (9)에 근거하여 설계되었다. 자화 인덕턴스 Lm은 74.27 μH, 공진 인덕턴스 Lr은 18.95 μH, 공진 커패시턴스 Cr은 133.67 nF이며, 이를 포함한 Prototype 회로의 주요 소자 파라미터를 Table 3에 정리하였다.

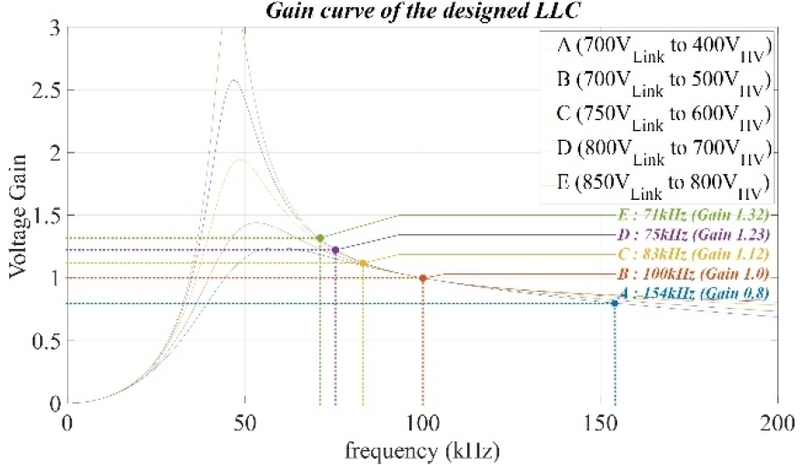

Fig. 10은 Table 3에 나열된 파라미터를 갖는 Half-Bridge LLC 공진 탱크의 전압 이득 곡선을 보여준다. 필요한 전압 이득의 범위는 최소 0.8 ~ 최대 1.32이며, 동작 주파수는 71 kHz에서 154 kHz이다. CC 구간인 VHV 400 ~ 500 V 구간에서 제안회로가 Above영역에서 동작하도록, 이 외의 구간인 CP 구간과 CV 구간에서는 공진 주파수 동작 및 Below영역에서 동작하도록 설계되었다.

4.2 실험 결과

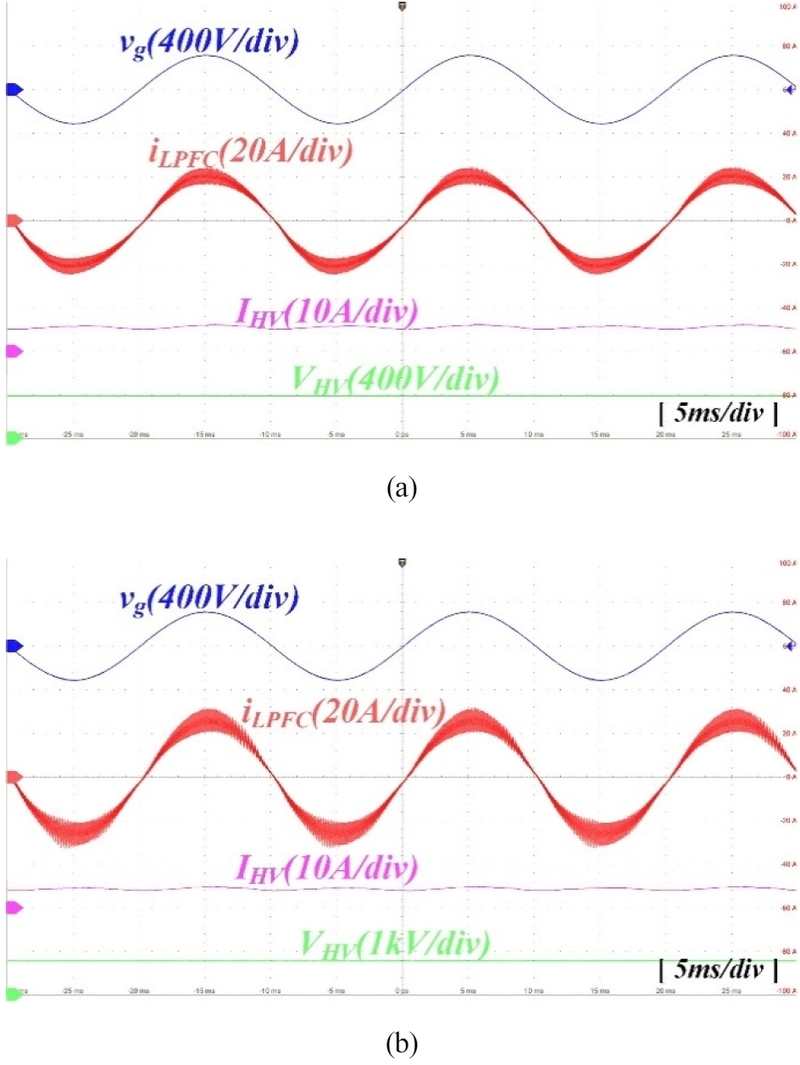

Fig. 11은 제안하는 단일 전력단 OBC의 정상상태 동작 파형을 보여준다. Fig. 11(a)의 최저 출력 전압인 VHV 400 V부터 Fig. 11(b)의 최고 출력 전압인 VHV 800 V까지 정상 동작이 가능하고, 출력 전류 IHV의 큰 저주파 변동 없이 HV 배터리 충전 동작 수행이 가능함을 확인할 수 있다.

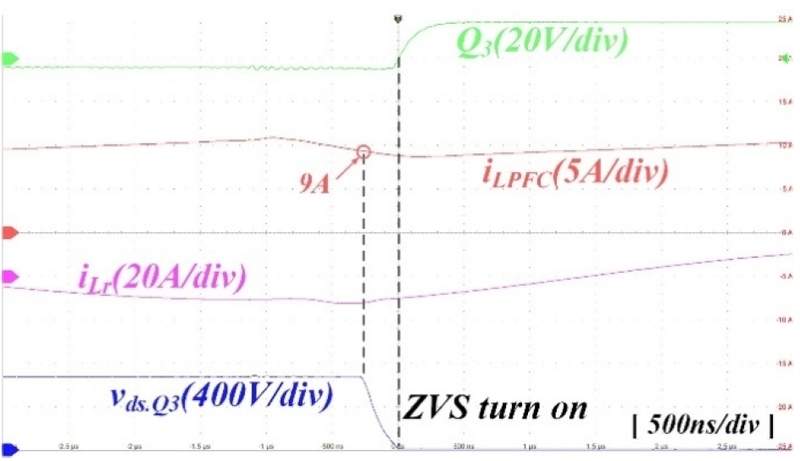

Fig. 12는 제안하는 단일 전력단 OBC를 구성하는 스위치 Q3의 ZVS 턴 온 성취 파형을 보여준다. 보다 정확한 ZVS 턴 온 동작 확인을 위해, OBC 입력 전압을 140 VDC, VLink를 700 V, VHV를 500 V로 고정하였고, 100 kHz 공진 주파수 동작하였다.

Q3의 Drain-to-Source 전압인 vds.Q3가 700 V에서 0 V로 하강하기 시작하는 시점의 iLPFC는 약 9 A로 측정되었고, Q3가 턴 온 되는 시점에 vds.Q3는 0 V로 완전히 하강하였음이 관측되었다. 이로써, 식 (8) 및 (9)에 근거한 제안하는 단일 전력단 OBC의 설계와 Partial ZVS 턴 온 성취가 유효함을 확인할 수 있다.

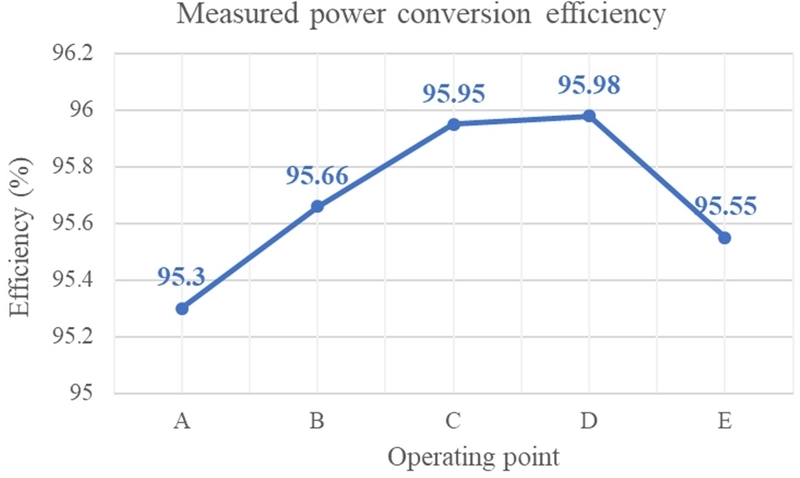

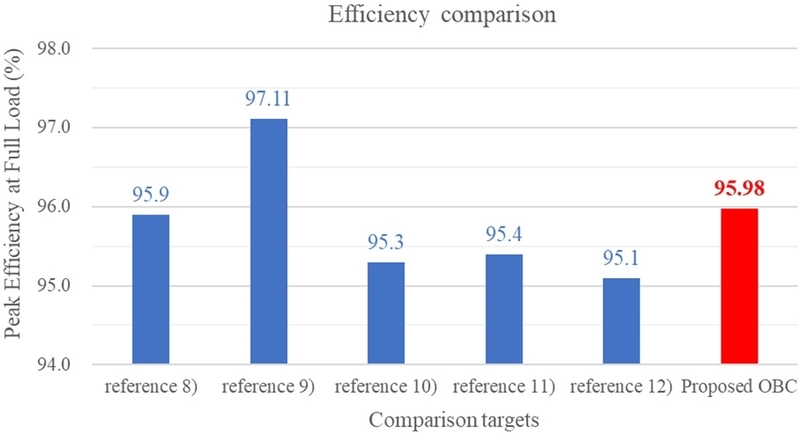

Fig. 13은 Prototype 회로 실험의 효율 측정 결과를 보여준다. 최대 효율은 95.98 %로 나타났으며, 이로써, 제안하는 단일 전력단 OBC는 MOSFET 소자 통합 및 수를 저감하였음에도 고효율 전력 전달이 가능하다고 할 수 있다.

Fig. 14는 제안하는 단일 전력단 OBC와 기존 연구 수행된 단일 전력단 OBC들의 전부하 조건에서 첨두 효율 비교 결과를 나타낸다. 제안하는 단일 전력단 OBC의 첨두 효율은 95.98 %이며, 참고 문헌 9)를 제외한 나머지 회로 및 제어 방식보다 높은 전력 변환 효율을 보여준다. 이로써, 제안하는 단일 전력단 OBC가 타 연구 성과보다 고효율 전력 전달이 가능함을 알 수 있다.

4. 결 론

본 논문에서는 MOSFET 소자 수 저감이 가능한 단일 전력단 OBC를 제안하였다. Inverter PFC와 Half-Bridge LLC 공진형 컨버터를 통합하여 단일 전력단 구조를 완성하였고, 스위치 소자가 통합된 스위칭 레그의 Partial ZVS 턴 온 달성 수식 분석 및 이를 고려한 공진부 설계를 진행하였다. 또한, Prototype 회로 실험을 통해 400 ~ 800 V 전체 출력 범위의 정상 동작 및 제안 회로의 동작 가능성을 확인하였고, ZVS 턴 온 성취 파형을 통해 본 논문의 Partial ZVS 턴 온 달성 수식 분석의 정합성을 검증하였다. 결과적으로, 제안하는 단일 전력단 OBC 회로 구조를 활용한다면, MOSFET 소자 수 저감을 통한 회로 고밀도 설계와 고효율 전력 전달이 가능하다.

Subscripts

| CC : | constant current |

| CMI : | common-mode current |

| CMV : | common-mode voltage |

| CP : | constant power |

| CV : | constant voltage |

| EMI : | electromagnetic interference |

| EV : | electric vehicle |

| OBC : | on-board charger |

| PFC : | power factor correction |

| WBG : | wide bandgap |

| ZVS : | zero voltage switching |

Acknowledgments

이 논문은 인천대학교 2023년도 자체연구비 지원에 의하여 연구되었음.

References

-

R. Pradhan, N. Keshmiri and A. Emadi, “On-Board Chargers for High-Voltage Electric Vehicle Powertrains: Future Trends and Challenges,” IEEE Open Journal of Power Electronics, Vol.4, pp.189–207, 2023.

[https://doi.org/10.1109/OJPEL.2023.3251992]

-

A. Khaligh and M. D'Antonio, “Global Trends in High-Power On-Board Chargers for Electric Vehicles,” IEEE Transactions on Vehicular Technology, Vol.68, No.4, pp.3306–3324, 2019.

[https://doi.org/10.1109/TVT.2019.2897050]

-

Y. -S. Kim, C. -Y. Oh, W. -Y. Sung and B. K. Lee, “Topology and Control Scheme of OBC–LDC Integrated Power Unit for Electric Vehicles,” IEEE Transactions on Power Electronics, Vol.32, No.3, pp.1731–1743, 2017.

[https://doi.org/10.1109/TPEL.2016.2555622]

-

N. Keshmiri, D. Wang, B. Agrawal, R. Hou and A. Emadi, “Current Status and Future Trends of GaN HEMTs in Electrified Transportation,” IEEE Access, Vol.8, pp.70553–70571, 2020.

[https://doi.org/10.1109/ACCESS.2020.2986972]

-

P. He, A. Mallik, A. Sankar and A. Khaligh, “Design of a 1-MHz High-Efficiency High-Power-Density Bidirectional GaN-Based CLLC Converter for Electric Vehicles,” IEEE Transactions on Vehicular Technology, Vol.68, No.1, pp.213–223, 2019.

[https://doi.org/10.1109/TVT.2018.2881276]

-

B. Li, Q. Li, F. C. Lee, Z. Liu and Y. Yang, “A High-Efficiency High-Density Wide-Bandgap Device-Based Bidirectional On-Board Charger,” IEEE Journal of Emerging and Selected Topics in Power Electronics, Vol.6, No.3, pp.1627–1636, 2018.

[https://doi.org/10.1109/JESTPE.2018.2845846]

-

C. -Y. Oh, D. -H. Kim, D. -G. Woo, W. -Y. Sung, Y. -S. Kim and B. -K. Lee, “A High-Efficient Nonisolated Single-Stage On-Board Battery Charger for Electric Vehicles,” IEEE Transactions on Power Electronics, Vol.28, No.12, pp.5746–5757, 2013.

[https://doi.org/10.1109/TPEL.2013.2252200]

-

J. Yuan, A. Poorfakhraei, Y. Zhang, G. Fang and A. Emadi, “A Novel Sinusoidal Extended Phase Shift Modulation With Minimal Loss for Single-Stage Onboard Chargers for Electrical Vehicles,” IEEE Journal of Emerging and Selected Topics in Industrial Electronics, Vol.6, No.2, pp.574–584, 2025.

[https://doi.org/10.1109/JESTIE.2024.3495665]

-

H. Kim, J. Park, J. Lee and S. Choi, “A Simple Modulation Strategy for Full ZVS of Single-Stage Electrolytic Capacitor-Less EV Charger With Universal Input,” IEEE Transactions on Power Electronics, Vol.37, No.10, pp.12030–12040, 2022.

[https://doi.org/10.1109/TPEL.2022.3165182]

-

J. Yuan, A. Poorfakhraei, Y. Zhang, G. Fang, C. Liu and A. Emadi, “An Improved Adaptive Sinusoidal Single Phase Shift Modulation for Bidirectional Single-Stage Onboard EV Chargers,” IEEE Transactions on Transportation Electrification, Vol.10, No.3, pp.5867–5879, 2024.

[https://doi.org/10.1109/TTE.2023.3324885]

-

D. Zinchenko, A. Blinov, A. Chub, D. Vinnikov, I. Verbytskyi and S. Bayhan, “High-Efficiency Single-Stage On-Board Charger for Electrical Vehicles,” IEEE Transactions on Vehicular Technology, Vol.70, No.12, pp.12581–12592, 2021.

[https://doi.org/10.1109/TVT.2021.3118392]

-

S. -G. Jeong, Y. -S. Jeong, J. -M. Kwon and B. -H. Kwon, “A Soft-Switching Single-Stage Converter With High Efficiency for a 3.3-kW On-Board Charger,” IEEE Transactions on Industrial Electronics, Vol.66, No.9, pp.6959–6967, 2019.

[https://doi.org/10.1109/TIE.2018.2877093]