효과적인 FMEDA 수행을 위한 안전 메커니즘의 작성 방안과 진단 커버리지의 산정 방안

* This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License(http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium provided the original work is properly cited.

Abstract

When the vehicle E/E systems were developed to comply with over ASIL B level on ISO 26262, FMEDA should be executed in order to evaluate the SPFM, LFM, and PMHF. The items to be considered when conducting FMEDA are the base failure rates with regard to HW elements and the distribution-rates of failure mode, as well as determining whether the HW element is safety related or not. If the failure mode of the safety related HW element is likely to violate the safety goal, the single-point/residual/latent fault should be classified according to the type of safety goal violation. In addition, there is also a study on safety mechanisms, which technical means to defend or avoid failure modes for HW elements that could violate the safety goal. The numerical expression of how effective these safety mechanisms can defend the failure mode of an HW element that could violate the safety goal is the diagnostic coverage(DC). The higher the DC, the better the performance of the safety mechanism. It is also very helpful in reaching the quantitative target value for the vehicle E/E system. Therefore, it is very important to estimate the DC for safety mechanisms. Unfortunately, there is not enough useful reference to estimate the DC value. Moreover, the content described in Annex D of ISO 2662-5: 2011 can be misleading. In this paper, we recognized the misconceptions about the “Evaluation of diagnostic coverage” in ISO 26262-5: 2011 Annex D, and examined how to use the safety mechanisms in FEMDA. Furthermore, we suggested the method of estimating the DC of the safety mechanism and how to define the safety mechanism.

Keywords:

E/E System, ISO26262 Functional safety, Failure modes effects and diagnostics analysis, SM, Diagnostic coverage, Probabilistic metric for random HW failures, HW Architecture metric, Single point fault metric, Latent fault metric키워드:

전기/전자 시스템, 기능안전, 고장모드 영향 및 진단 분석, 안전 메커니즘, 진단 커버리지, 하드웨어 우발 고장 확률 지표, 하드웨어 아키텍처 지표, 단일점 결함 지표, 잠재 결함 지표1. 서 론

기능안전 ISO 26262를 준수하는 제품 설계에 부여된 안전 목표를 충족시키는데 필요한 실질적 수단은 안전 설계를 실현 하는 것이다.

안전 설계를 실현하기 위해서는 IATF16949, CMMI(Capability Maturity Model), A-SPICE와 같은 표준 프로세스 구축 및 이행을 통한 강건한 프로세스의 실현과 외란 및 내외부의 잡음에 둔감하기 위한 강건 설계, 그리고 의도하지 않은 기능의 종료 또는 전개를 억제하거나 예방하기 위한 안전메커니즘의 구현이다. 그 뿐만 아니라 Systematic failure를 예방하기 위한 시스템, 하드웨어, 소프트웨어 각 개발 단계에서의 안전 분석 이행 역시 필요하다.

본 논문은 안전 설계를 실현하기 위한 수단 중 하나인 안전메커니즘에 대하여 안전메커니즘을 기술하는 방안 및 안전메커니즘에 대한 진단 커버리지 산정 방안을 제시하고, 진단 커버리지 산정에 있어 중요 참고 문서인 ISO26262-5:2011의 부속서 D, 진단 커버리지의 평가에 대한 오해의 소지를 살펴본다.

2. 본 론

2.1 DC 산정을 위한 협업의 필요성

ISO26262-1:2011, 2.111에서 안전메커니즘은 결함(Faults)을 검출하거나 고장(Failures)을 제어함으로써, 안전한 상태(Safe state)에 도달하거나 유지하기 위하여 전기/전자장치 기능이나 엘리먼트 또는 기타 기술로 구현된 기술적 해결책으로 정의 된다.1)

이러한 안전메커니즘의 구현은 하드웨어 단독이거나 소프트웨어 단독으로도 물론 가능 하지만, 대개의 경우 하드웨어와 소프트웨어 간의 조합으로 구현된다. 심지어 일부는 기구물과의 조합으로도 이루어질 수가 있다. 그러하기 때문에 안전메커니즘에 대한 진단 커버리지를 산정하기 위해서는 하드웨어 담당자 단독으로 해서는 안 되며, 시스템, 하드웨어, 소프트웨어 담당자가 서로 유기적으로 협력하여 수행될 필요가 있다.

2.2 FMEDA에서 안전메커니즘의 쓰임

안전메커니즘의 설계 및 사용에 대한 일반적인 목적은 의도한 기능이 정상적으로 작동함을 보장하고, 의도하지 않는 기능의 전개를 발생하지 않게 하기 위함이다. 이를 위해 안전메커니즘은 결함을 감지하고 감지된 결함을 회피 또는 방지하거나 예방 하기 위한 활동을 수행한다.

Watch-dog Timer, Voltage/Current Monitoring, Clock Monitoring, Input comparison/voting, CRC Checker, ECC(Error Correcting Code), 하드웨어 redundancy (e.g. Dual Core Lockstep, Asymmetric redundancy, Coded processing) 등, 정말 많은 타입의 안전메커니즘이 존재하며, 이러한 안전메커니즘은 굳이 기능안전 측면이 아니어도 일반적인 설계에서 전통적으로 흔히들 사용 되고 있다.

하지만, FMEDA에서 안전메커니즘의 쓰임은 하드웨어 엘리먼트의 고장 모드가 안전 목표 또는 안전 요구사항을 위반하는 경우, 이를 예방하거나 회피하기 위한 것이다. 이는 안전메커니즘이 차량 E/E System에 존재하는 단일점 결함율과 다중점 잠재 결함율을 억제한다는 것으로 해석 될 수 있다.

2.3 ISO 26262-5:2011 부속서 D의 오해 소지

ISO26262-5:2011 부속서 D에 기술된 진단 커버리지의 평가는 진단 커버리지 산정 및 중간 수준의 복잡도를 갖는 하드웨어 엘리먼트들에 대한 고장 모드를 식별하는데 있어서, 개발 초기에 매우 유용한 도움을 주는 것은 분명하다. 왜냐하면 각 하드웨어 엘리먼트 별로 대부분의 고장 모드가 기술되어 있으며, 진단 커버리지 값을 Low(60 %), Medium(90 %), High(99 %)로 구분하였기 때문이다.

하지만, ISO 26262:2011-5 부속서 D에 기술 된 진단 커버리지의 평가는 중대한 결함이 있다. 이는 기술된 고장 모드에 대해 안전 목표 또는 안전요구사항을 위반할 가능성에 대한 고려가 없음을 의미한다.

안전메커니즘에 대한 진단 커버리지를 산정할 때 가장 중요한 고찰은 해당 안전메커니즘의 역량이 안전 목표 또는 안전 요구사항을 위반하는 하드웨어 엘리먼트의 결함을 얼마만큼 커버할 수 있는지를 파악하는 것이다.

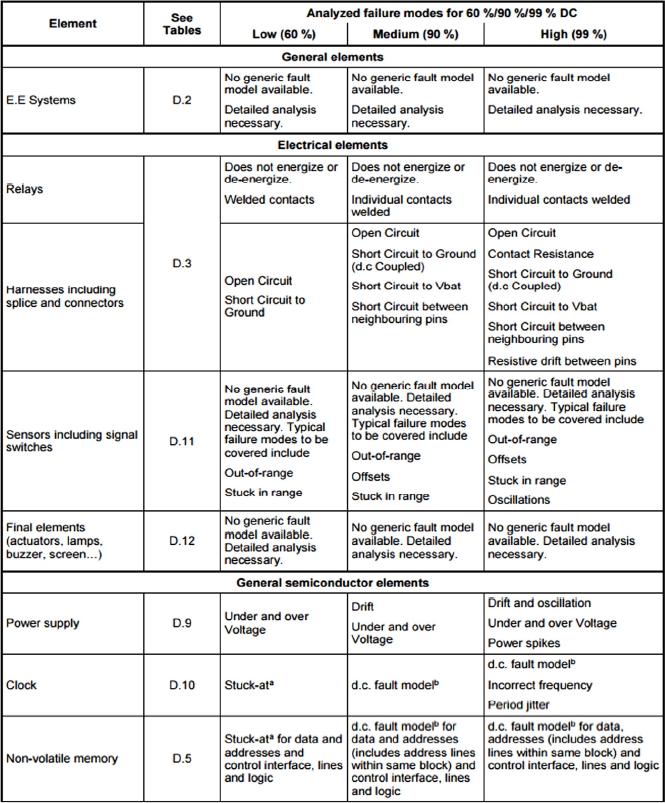

그러나, ISO26262-5:2011 Annex D Table D.1에 기술된 내용은 하드웨어 엘리먼트의 고장 모드가 안전 목표 또는 안전요구사항을 위배 하는지에 대한 고찰 없이 단지, 커버되는 고장 모드의 개수가 많을수록 진단 커버리지의 값이 증가 되는 것으로 표현하고 있다. 아래 ISO26262-5:2011 Annex D Table D.1 일부를 발췌한 Table 1을 보게 되면, 각 개별 하드웨어 엘리먼트 별로 DC가 Low(60 %)에서 High(99 %)로 분류될수록 기술된 고장 모드들이 대부분 중첩됨을 볼 수 있다.

이것은 FMEDA를 수행하는데 있어서 안전메커니즘의 진단 커버리지를 산정할 때 크나큰 오해를 불러일으킬 수 있다. 왜냐하면, 안전메커니즘이 방어하는 하드웨어 엘리먼트의 고장 모드가 안전 목표를 위배하지 않는다면, 그 하드웨어 엘리먼트의 고장은 결과적으로 안전측 고장이 됨으로, 이 하드웨어 엘리먼트의 고장 모드를 방어 하는 안전메커니즘은 기능안전 측면에서 아무 일도 하지 않는 것과 마찬 가지가 되기 때문이다. 다시 말해서 이 경우의 진단 커버리지의 값은 0 %가 된다는 것이다.

이해를 돕기 위해 ISO 26262-5:2011 부속서 D Table D.1의 일부를 수정한 예를 Table 2에 들겠다.

- ① 하드웨어 엘리먼트에 대한 고장 모드와 고장 모드 별 분배율을 구한다.

● R/L/C 및 Description 소자와 같은 하드웨어 파트의 경우는 IEC TR 62380:2004 또는 IEC 61709: 2017과 같은 고장 데이터 북을 참조하고,4,5)

● Regulator와 같은 중간 수준의 복잡도를 갖는 하드웨어 엘리먼트의 경우는 ISO 26262-5, 부속서 D를 참조할 수 있다.1,2) - ② 분석되고 식별된 하드웨어 엘리먼트의 고장 모드 각각에 대하여 안전목표(SG)를 위반하는지에 대한 여부를 체크한다.

- ③ 안전메커니즘(SM)이 Cover 할 수 있는 것이 무엇인지를 확인하여 DC 값을 계산한다.

● SM이 Over voltage와 Drift를 모두 Cover 한다면, DC = 100 %

● SM이 Over voltage만 Cover 한다면, DC = Over(30 %) / {Over(30 %) + Drift(30 %)} = 50 %

● SM이 Over voltage와 Drift만 제외하고 모두 Cover 한다면, DC = 0 %

ISO26262-5:2011 부속서 D에서 진단 커버리지 값을 60 %, 90 %, 99 %로 3 가지로서만 산정하였던 것을 위의 예시를 통해 보다 세밀한 진단 커버리지 값 산정이 가능함을 알 수 있다. 뿐만 아니라, 중간 수준의 복잡도를 갖는 하드웨어 엘리먼트에 대한 고장 모드 분포율에 대하여서도 역시 보다 세밀한 분포율을 산정할 수 있음을 알 수 있다.

하지만, 위의 예시에서 단점이 존재하는데, 이는 특정 하나의 고장 모드 자체에 대한 평가가 아닌, 하드웨어 엘리먼트가 가지는 가능한 모든 고장 모드에 대하여 일괄 취급하여 평가 됐다는 것이다. 앞서 기술한 바와 같이 안전메커니즘에 대한 진단 커버리지 값을 산정하기 위해서는 분석된 고장 모드 하나를 기준으로 안전 목표 또는 안전요구사항을 위반할 가능성에 대한 평가를 수행 하여야만 보다 정확한 진단 커버리지 값 산정이 가능하다.

2.4 안전메커니즘의 DC 값을 산정하기 위한 방안 및 사례

안전메커니즘의 진단 커버리지 값은 HARA(Hazard Analysis and Risk Assessment) 분석의 결과로 도출된 안전 목표와 더불어 장치 설계 방식에 크게 의존된다. 그러하기 때문에,

첫째, 시스템에 대한 완전한 이해가 필요하다.

둘째, 안전 목표를 위반할 가능성이 있는 하드웨어 엘리먼트의 고장 모드를 식별해야 한다. 이것은 FMEA(Failure Mode and Effect Analysis), FTA(fault Tree Analysis), DFA(Dependent Failure Analysis)와 같은 안전분석을 통해 식별할 수 있다.

셋째, 안전 목표를 위반할 가능성이 있는 하드웨어 엘리먼트의 고장 모드를 안전메커니즘이 방어 하는 경우, 그 안전메커니즘이 방어하지 못하는 구간을 찾는 것이다. 이것은 아래와 같은 수식을 통해 구할 수가 있다.

DC(Diagnostic Coverage)% = DDFF / DFF = 1 - (DUFF / DFF) .............. (수식 1)

● DFF = DDFF + DUFF

● DFF : Dangerous Fault Factor

● DDFF: Dangerous Fault but Detected Fault Factor

● DUFF: Dangerous Fault Factor and Undetected Fault Factor

아래는 이에 대한 예시이다.

Ex1)

- a. 결함이 나더라도 안전 목표를 위배하지 않는 구간

- b. 결함이 발생되면 안전 목표를 위배할 가능성이 있으나, 안전메커니즘이 충분히 방어할 수 있는 구간

- c. 결함이 발생되면 안전 목표를 위배할 가능성이 있으나, 안전메커니즘이 방어하지 못하는 구간

- d. 수식 1에 의해 DC (%) = b/(b+c) = 1-(c/(b+c))

‘a’. 구간은 안전측 결함으로써 ISO/DIS 26262-11에서 제안된 Amount of Safety fault2)에 해당되기 때문에, 위 수식에서 제외하였다.

다른 예로서 통신 모니터링 및 클록 모니터링에 대한 진단 커버리지 산정 방안 예를 Ex2), Ex3)에 각각 제시한다. 참고로 Ex2)는 ISO/DIS 26262-11부속서 A를 참조하였음을 밝힌다.

Ex2)2)

[Assumption] : 4 비트 ID와 16 비트 CRC를 사용하는 디지털 통신에서 안전 목표를 위반하는 고장 모드가 “수신된 데이터의 훼손”이라면 안전메커니즘의 DC는 다음과 같이 산정 될 수 있다.

DC(%) = 1- ((1/2^4) * (1/2^16)) = 99.9 %

Ex3)

[Assumption] : 하드웨어 방식의 클록 카운팅을 통하여 클럭에 대한 모니터링을 할 수 있는 안전메커니즘이 2.5 %의 오차율이 존재하고 안전 목표를 위반할 가능성이 있는 고장 모드가 Jitter와 stuck at fault라면,

● Jitter의 경우 DC(%) = 1 - 0.025 = 97.5 %,

● Stuck at fault의 경우 DC(%) = 99 % 또는 100 %로 산정할 수 있다.

산정할 수 있는 안전메커니즘의 진단 커버리지 값의 범위는 0 % 초과 100 % 이하이다. 0 %일 경우, 안전메커니즘이 존재하지 않는 것과 동일하나, 이와는 반대로 100 %일 경우, 잔존 결함이 0 %가 되면서 단일점 결함을 완전히 해결 했다고 볼 수 있다.

여기서 100 %를 갖는 진단 커버리지 값에 대하여 생각해 볼 것은 보다 보수적으로 평가하기 위하여 1 % 내외를 제외할 수 있다는 것이다. 이는 안전 목표를 위배하는 하드웨어 엘리먼트의 고장 모드에 대해 안전메커니즘이 얼마만큼 커버할 수 있는가에 대한 분석이 완벽할 수 없는 경우를 상기한다면 1 % 내외를 제외함으로서, 부족한 분석에 대한 일부분을 약간이나마 보완할 수 있다고 판단된다.

그리고 이와는 별개로 Ex3)의 예를 통해 하나의 안전메커니즘이 고장 모드에 따라 진단 커버리지 값을 개별로 가져 갈 수 있음을 확인하였다.

그 밖에 사례로서 SAE(Society of Automotive Engineers)에 기재된 논문인 “Diagnostic Coverage Evaluation Method for Analog Circuits to Comply with Functional Safety Standard.” 를 간략하게 소개한다.3)

위 논문은 저항 R1과 저항 R2로 구성된 전압 분배회로에 의해 출력된 아날로그 전압 Vo를 하드웨어로 구성된 비교기에 의해 상시 모니터링하여 기준 전압 이상일 때 회로를 차단하는 안전메커니즘에 대한 진단 커버리지 값을 산출 하는 방법을 제시하였다. 이를 위해

step1. 안전메커니즘이 커버하는 대상 회로에 대한 안전 작동 조건과 위험 작동 조건을 정의하였으며,

step2. 안전메커니즘이 커버하는 대상 회로의 각 하드웨어 요소에 대한 Fault model을 정의하였고,

step3. 저항 R1과 저항 R2에 대한 결함 주입 시뮬레이션을 통해 결함 영역을 분류하였고,

step4. 결함 분류 결과로 DC를 산출하였다.

특이할 점으로서 Sep1에서 안전메커니즘의 안전 작동 조건과 위함 작동 조건을 정의 할 때, 안전 목표 위배 여부에 따라

● Safe condition,

● Hazardous and covered condition,

● Hazardous and uncovered condition

위 3가지로 구분한 것이다. 이러한 구분은 step3에서 저항 R1과 저항 R2에 대한 결함 주입 시뮬레이션을 토대로 결함 영역을 아래와 같이 분류 하는데 사용된다.

● SF(Safe Fault) region,

● HDF(Hazardous Detectable Fault) region,

● HUF(Hazardous Undetectable Fault) region

위 3가지 영역이 차지하고 있는 면적 비율을 구하고, 이를 ISO26262-5:2011, Annex C에 설명되어진 공식을 적용하여 결국, Table 3과 같은 결과를 도출하게 된다.

“Diagnostic Coverage Evaluation Method for Analog Circuits to Comply with Functional Safety Standards,” Table 4. DC of each fault model and DC of functional block3)

Table 3을 보게 되면, 안전 목표를 위배하는 저항 R1과 R2의 Fault model 별로, DC가 각각 산정됨을 볼 수 있으며, 또한 표 하단 부의 Functional block(Total)에서 해당 안전메커니즘 전체에 대한 DC 값을 볼 수 있다.

보다 상세한 도출 과정은 본문에서 밝히는 것이 적절치 않으며, 이를 위해 해당 논문을 직접 읽어 보는 것을 권한다.

2.5 안전메커니즘의 기술 방안

기능안전 ISO 26262를 준수하는 제품 개발에서 안전메커니즘의 구현은 시스템 개발 단계인 TSC (Technical Safety Concept)에서 처음 고려되어 각 개발 단계에서 구체화되고 실현된다. 이 과정에서 TSC는 안전메커니즘을 전체 시스템 수준에서 관리할 수 있다. 즉, TSC에서 안전메커니즘에 대한 속성 및 구현 방안에 대하여 기술할 수 있다는 것이다. 물론, 시스템 개발 초기 단계에서 안전메커니즘에 대한 세부적이고 구체적인 기술은 어려울 수 있겠으나, 하드웨어 및 소프트웨어 개발 단계에서 이를 보완하여 반복 갱신함으로서 안전메커니즘에 대한 내용이 완벽해 질 수 있다.

아래의 Table 4는 안전메커니즘을 기술하기 위한 제안된 양식과 그 설명이다.

- ① 추적성 확보를 위한 안전메커니즘의 ID

- ② 안전메커니즘의 명칭

● Ex) 차량 배터리 전압 모니터링 - ③ Operation Time: 작동 시간, FTTI(Fault Tolerant Time Interval) 및 FRT(Fault Reaction Time), MPFDI(Multiple Point Fault Detection Interval), FDT(Fault Detection Time) 등과 관련이 있는 안전메커니즘의 동작 시간을 기입

- ④ 안전메커니즘을 구현하기 위한 파트를 기입

● Ex) HW & Software part - ⑤ 안전메커니즘 동작의 결과로서 안전 상태를 기입

● Ex) (정상 범위를 벗어난 배터리 전원 상태일 경우) CAN 메시지 송출 금지 - ⑥ 안전메커니즘이 방어하는 엘리먼트의 고장 모드를 기입

● Ex) 저전압, 고전압 상태 감지 - ⑦ 안전메커니즘의 진단 커버리지 값을 기입

● ISO26262-5 부속서 D에 기술된 DC 값은 시작점 즉, 개발 초기에 사용할 수 있으나 이후에는 보다 정밀한 분석을 통한 DC 값을 기입한다. - ⑧ 진단 커버리지를 산정한 근거를 간략 기술

● ISO26262-5 부속서 D에 기술된 DC 값은 시작점 즉, 개발초기에 사용할 수 있으나 이후에는 보다 정밀한 분석을 통한 DC 산출 근거를 기입한다. - ⑨ 안전메커니즘의 유형을 기입

● 차량 E/E System에 존재하는 단일점 결함을 방어하기 위한 것과, 다중점 잠재 결함을 방어하는 것이 있으며, 또는 위의 둘 모두를 방어할 수 있는 것이 있음 - ⑩ 안전메커니즘의 기능을 간략 기술

● Ex) 정상 범위를 벗어난 배터리 전원 입력 시 CAN 메시지 송출을 금지하여 잘못된 정보 전달을 차단 - ⑪ 양방향 추적성을 위한 관련 안전 목표 정보 기입

● SG ID 및 내용을 기술 - ⑫ 양방향 추적성을 위한 관련 TSR 정보 기입

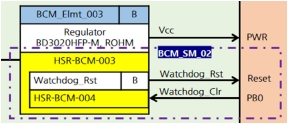

● TSR ID 및 내용을 기술 - ⑬ 안전메커니즘에 대한 아키텍처를 기입

● Ex) 블록 다이어그램, 순서도, 상태도 - ⑭ 아키텍처 설명 및 안전메커니즘의 동작 내용을 상세히 기술

3. 결 론

FMEDA는 분석이 완전할수록 정확도가 향상되는 분석 기법으로서, 안전메커니즘의 진단 커버리지를 보다 정확하게 산정하는 것이 FMEDA의 정확도를 향상시키는데 매우 큰 요인으로 차지한다.

본 논문은 안전메커니즘의 진단 커버리지를 산정하기 위한 방법과 안전메커니즘을 기술하는 방법을 제시함으로서 안전메커니즘에 대한 올바른 이해를 도모하였고, 결과적으로 이것은 FMEDA의 분석에 대한 정확도를 향상시키는 데 기여할 것으로 기대한다.

그리고 예시된 각 사례는 완전한 것이 아니며, HARA(Hazard Analysis and Risk Assessment) 분석의 결과로 도출된 안전 목표 및 제품의 설계 방식에 따라 달라질 수 있음을 밝힌다.

Nomenclature

| FMEDA : | failure modes effects and diagnostics analysis |

| SM : | safety mechanism |

| DC : | diagnostic coverage |

| E/E System : | electric/electronic system |

| PMHF : | probabilistic metric for random HW failures |

| HAM : | HW architecture metric |

| SPFM : | single point fault metric |

| LFM : | latent fault metric |

| SG : | safety goal |

| HW : | hardware |

References

- ISO Standard, ISO 26262 Road Vehicles - Functional Safety, (2011).

- Draft International Standard ISO/DIS 26262-11, Road Vehicles - Functional Safety - Part 11: Guideline on Application of ISO26262 to Semiconductors, (2016).

- R. Inada, T. Hirotsu, Y. Morita, and T. Hata, “Diagnostic Coverage Evaluation Method for Analog Circuits to Comply with Functional Safety Standards”, SAE 2015-01-0267, (2015).

- International Electrotechnical Commission, IEC TR 62380 Edition 1.0: Reliability Data Handbook - Universal Model for Reliability Prediction of Electronics Components, PCBs and Equipment, IEC, (2004).

- International Electrotechnical Commission, IEC 61709 Edition 3.0: Electric components - Reliability - Reference Conditions for Failure Rates and Stress Models for Conversion, IEC, (2017).